# MOS混載相変化不揮発性メモリの設計技術と高性能化に関する研究

|       |                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------|

| メタデータ | 言語: Japanese<br>出版者:<br>公開日: 2017-10-05<br>キーワード (Ja):<br>キーワード (En):<br>作成者: 高田, 雅史<br>メールアドレス:<br>所属: |

| URL   | <a href="http://hdl.handle.net/2297/3805">http://hdl.handle.net/2297/3805</a>                           |

# 博士論文

## CMOS 混載相変化不揮発性メモリの 設計技術と高性能化に関する研究

金沢大学大学院自然科学研究科

電子情報科学専攻

学籍番号 0423112103

氏名 高田 雅史

主任指導教員名 ..... 北川 章夫 助教授

|                         |    |

|-------------------------|----|

| 第1章 序論                  | 1  |

| 1－1 不揮発性メモリの需要背景        | 1  |

| 1－2 相変化不揮発性メモリの位置づけ     | 5  |

| 1－3 研究動向                | 9  |

| 1－3－1 開発企業              | 9  |

| 1－3－2 チップ集積化報告          | 9  |

| 1－3－3 大容量化に関して          | 12 |

| 1－3－4 低消費電力に関して         | 13 |

| 1－4 目的                  | 15 |

| 1－5 本論文の構成              | 16 |

| 第2章 カルコゲナイト半導体          | 19 |

| 2－1 始めに                 | 19 |

| 2－1－1 アモルファス物質          | 19 |

| 2－1－2 カルコゲナイト系アモルファス半導体 | 20 |

| 2－2 電気的特性               | 21 |

| 2－2－1 電気伝導度の温度依存性       | 21 |

| 2－3 相変化特性               | 22 |

| 2－3－1 相転移現象             | 22 |

| 2－3－2 相転移温度の昇温速度依存性     | 23 |

| 2－3－3 スイッチング現象          | 25 |

| 2－3－4 発振現象              | 26 |

| 2－4 モデル化                | 28 |

| 第3章 相変化不揮発性メモリ          | 34 |

| 3－1 記憶原理                | 34 |

| 3－2 メモリセル構造             | 36 |

| 3－3 メモリセルとしての性能         | 37 |

| 3－3－1 書き込み消去回数          | 37 |

| 3－3－2 書き換え速度            | 40 |

| 3－3－3 データ寿命             | 40 |

| 3－3－4 消費電力              | 43 |

| 3－4 メモリ回路構成             | 44 |

| 3－4－1 メモリセルアレイ          | 44 |

| 3－4－2 メモリ回路構成           | 45 |

| 3－5 回路設計                | 46 |

| 3－5－1 設計仕様              | 46 |

| 3－5－2 メモリセル設計           | 47 |

|                                  |           |

|----------------------------------|-----------|

| 3－5－3 メモリセル周辺回路 .....            | 49        |

| 3－5－4 読み出し回路設計 .....             | 49        |

| 3－5－5 書き込み回路設計 .....             | 50        |

| 3－5－6 メモリセルレイアウト .....           | 52        |

| 3－5－7 設計に考慮すべき諸問題 .....          | 52        |

| 3－5－8 対策回路 .....                 | 53        |

| 3－6 結言 .....                     | 55        |

| <b>第4章 多値化 .....</b>             | <b>56</b> |

| 4－1 目的 .....                     | 56        |

| 4－2 多値特性実験 .....                 | 57        |

| 4－3 読み出し回路設計 .....               | 59        |

| 4－3－1 読み出し方式 .....               | 59        |

| 4－3－2 回路構成及び動作 .....             | 60        |

| 4－3－3 シミュレーション .....             | 63        |

| 4－4 書き込み回路設計 .....               | 64        |

| 4－4－1 方式の検討 .....                | 64        |

| 4－4－2 回路構成及び動作 .....             | 65        |

| 4－4－3 書き込み動作 .....               | 69        |

| 4－4－4 シミュレーション .....             | 70        |

| 4－5 結言 .....                     | 73        |

| <b>第5章 PNSRAM .....</b>          | <b>74</b> |

| 5－1 背景 .....                     | 74        |

| 5－2 メモリセル構造 .....                | 77        |

| 5－3 メモリセル動作 .....                | 78        |

| 5－3－1 電源オフ／スタンバイ動作 .....         | 79        |

| 5－3－2 リコール動作 .....               | 79        |

| 5－3－3 初期化動作 .....                | 80        |

| 5－3－4 読み出し／書き込み動作 (SRAM動作) ..... | 82        |

| 5－3－5 ストア動作 .....                | 84        |

| 5－4 回路設計 .....                   | 85        |

| 5－4－1 仕様 .....                   | 85        |

| 5－4－2 メモリセル設計 .....              | 86        |

| 5－4－3 リコール安定化設計 .....            | 87        |

| 5－4－4 ストア動作安定化設計 .....           | 89        |

| 5－4－5 撃発読み出し動作安定化設計 .....        | 90        |

| 5－4－6 撃発書き込み動作安定化設計 .....        | 95        |

|                          |     |

|--------------------------|-----|

| 5-4-7 全体回路設計 .....       | 97  |

| 5-5 性能評価 .....           | 98  |

| 5-5-1 振発読み書き動作 .....     | 98  |

| 5-5-2 待機時消費エネルギー比較 ..... | 98  |

| 5-6 応用用途 .....           | 101 |

| 5-6-1 宇宙事業 .....         | 101 |

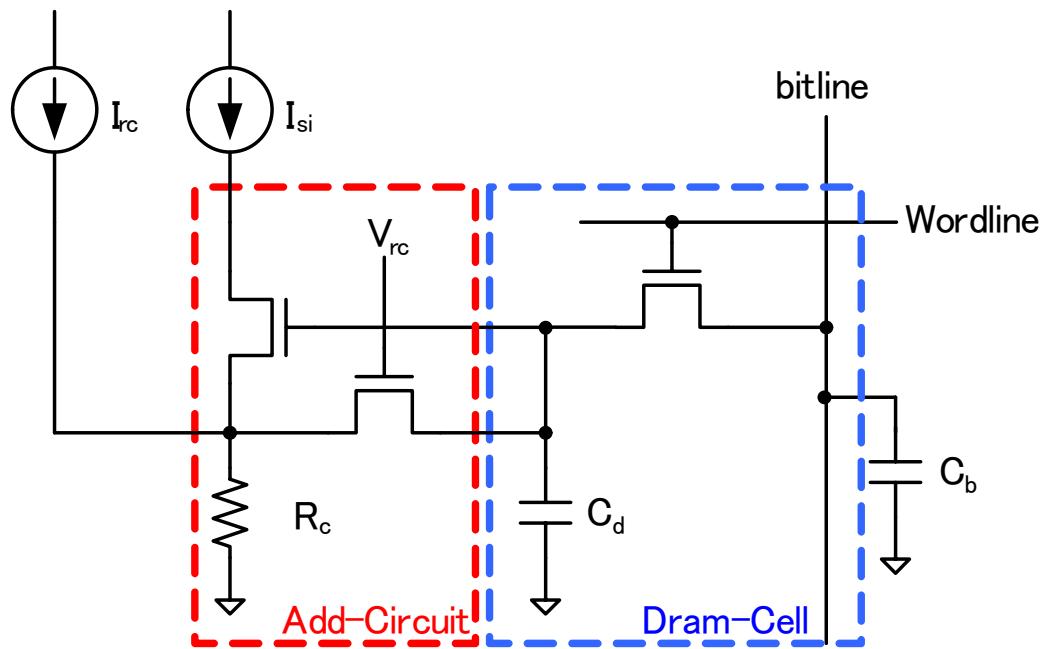

| 5-6-2 PNDRAM .....       | 102 |

| 5-7 結言 .....             | 105 |

| 第6章 結論 .....             | 106 |

| 6-1 本研究の総括 .....         | 106 |

| 謝辞 .....                 | 107 |

| 参考文献 .....               | 109 |

| 著者の主な研究業績目録 .....        | 113 |

# 第1章 序論

## 1-1 不揮発性メモリの需要背景

米調査会社カレント・アナリシスの調査によると、2006年5月に米国的小売市場ではノート型PCの需要がデスクトップ型PCを越え、さらに、同年同月、総務省が発表した「通信利用動向調査」によるとインターネットへのアクセス数がPCより携帯電話から行われる頻度が上回る等[1]、ユビキタス社会の実現に向け様々な携帯機器が着目されている。この様に需要が高まる携帯機器組込用LSI分野では、高速、高機能が求められ、製造プロセスの微細化により、1世代前の既存ロジックを、より高性能・小面積で実現することで要望に応えてきた。

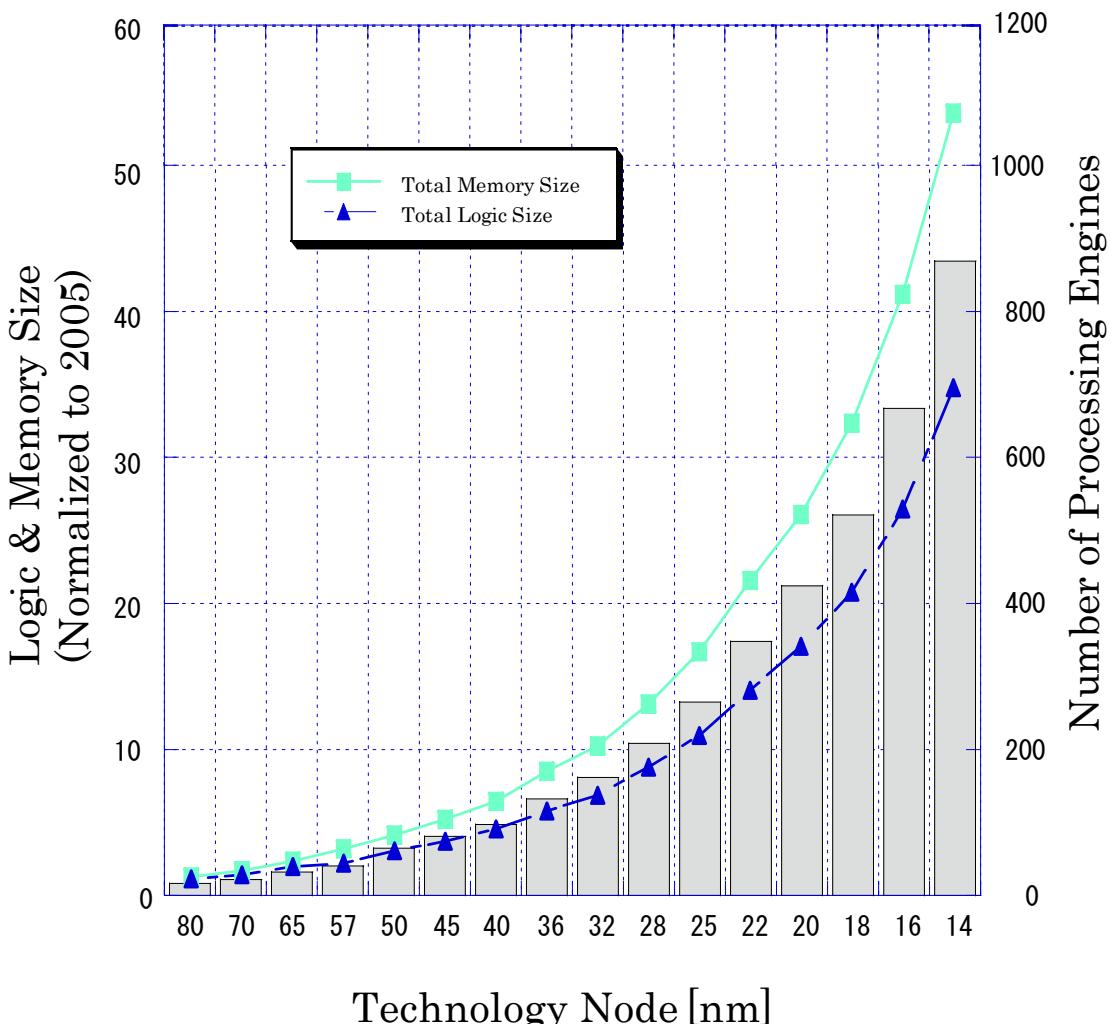

図 1-1 SoCにおけるデザインの複雑さ推移[1]

図 1-1に携帯機器組込用SoC(System on Chip)における設計について、その複雑さの傾向を表す図を示す[2]。横軸がTechnology Node、縦軸が設計における論理部とメモリ部のサイズ(折れ線部)、そして、PE(Processing Engine)の数の推移(棒線部)を示す。ただし、論理部とメモリ部のサイズに関しては、80nm Technology Node(2005年)に規格化されている。年々性能の向上を求められる為、CMOS技術の微細化に伴い、設計の複雑さは増していく。この設計の煩雑さは設計コストに繋がる。このコストを最小限にしつつ、性能を満たすための解として、機能ブロックのPE化が挙げられる。これは、並列処理と特定機能をもったハードウェアの実現によって、SOCの高い処理パフォーマンスと低消費電力の両立を可能にするからである。図 1-1中より、PE数の急速な増加予測に、IP(設計資産: Intellectual Property)化の有効性が見て取れる。この機構では、周回路は同じ複雑性を保ちながら、PE数の増加による性能向上は論理部とメモリ部面積の二次関数的増加を引き起こす。特にメモリ部の増加は著しいことも同様に図 1-1より見て取れる。

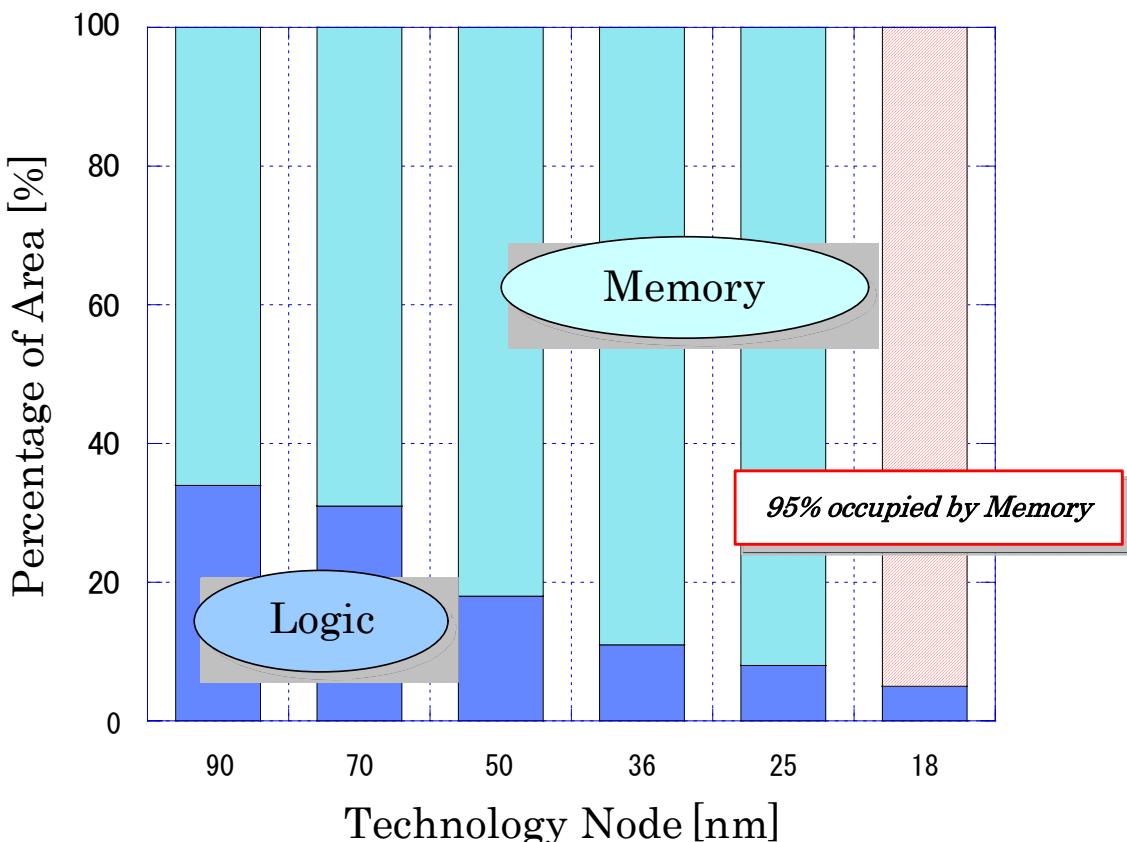

図 1-2 SoCにおけるメモリ占有面積比率の推移[2]

図 1-2に携帯機器用SoC(Die Size 100mm<sup>2</sup>仮定)における論理部とメモリ部の面積比を示す[2]。横軸がTechnology Node、縦軸が各占有面積である。図 1-1では、80nm CMOS

Sプロセスによって規格化された、論理部、メモリ部の面積増加率を示したが、事実、その面積比は大きく異なっている。図 1-2に示すように、チップ全体において、メモリ部の面積が論理部の面積に比べ、増大する傾向が予測されている。これは図 1-1においても、メモリ部の面積増加率の成長は論理部に比べ、年々引き離す予測が成されていることからも分かる。図 1-2によると 18nm Technology Node(2018 年)においては、95% ものチップ領域がメモリ部に占められると予測されている。

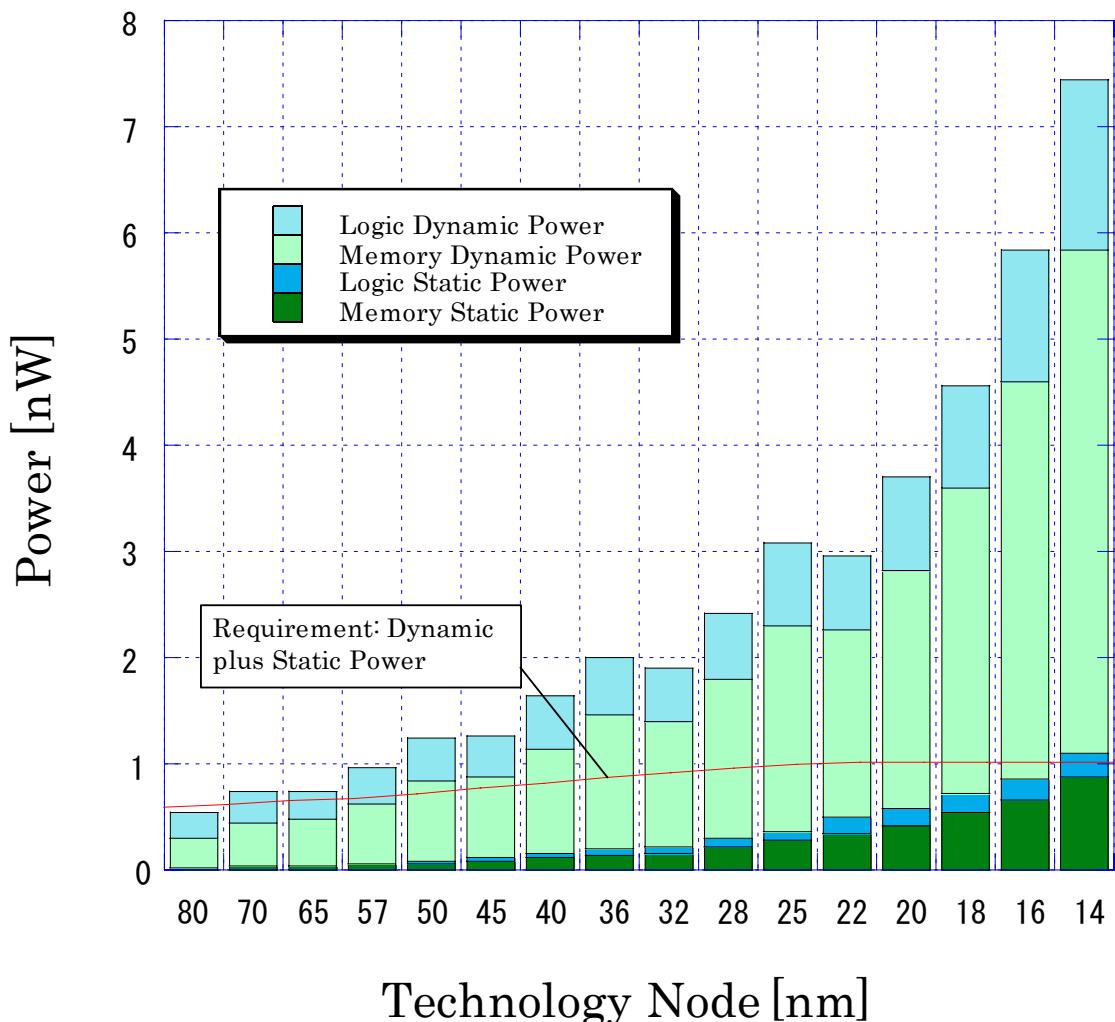

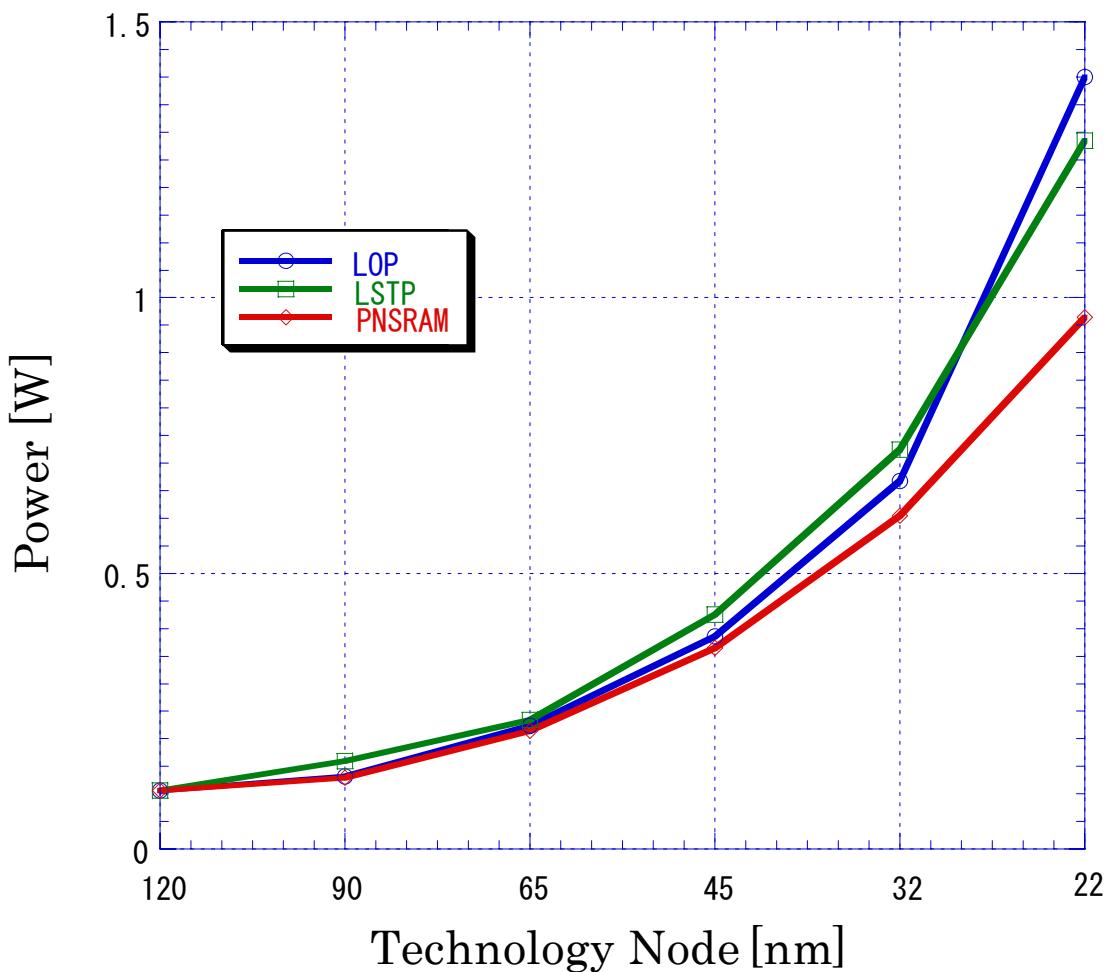

図 1-3 SoCにおける動的／静的消費電力の推移[2]

現在、この組込用メモリ開発において、最も求められる仕様が消費電力であり、消費電力によって他の性能、機能が定められると言っても過言ではない。図 1-3に携帯機器用 SoCにおける論理部、メモリ部それぞれに対する、動的／静的消費電力を示す[2]。横軸が Technology Node、縦軸が消費電力予測、そして、図中の線が要求される消費電力である。図から読み取れるように、このままでは要求条件を全く満たすことが出来ない。そこで、

携帯機器分野では、性能よりも動作時の消費電力削減を優先し、LOP（低消費電力仕様）と呼ばれる仕様を採用されてきた[4].

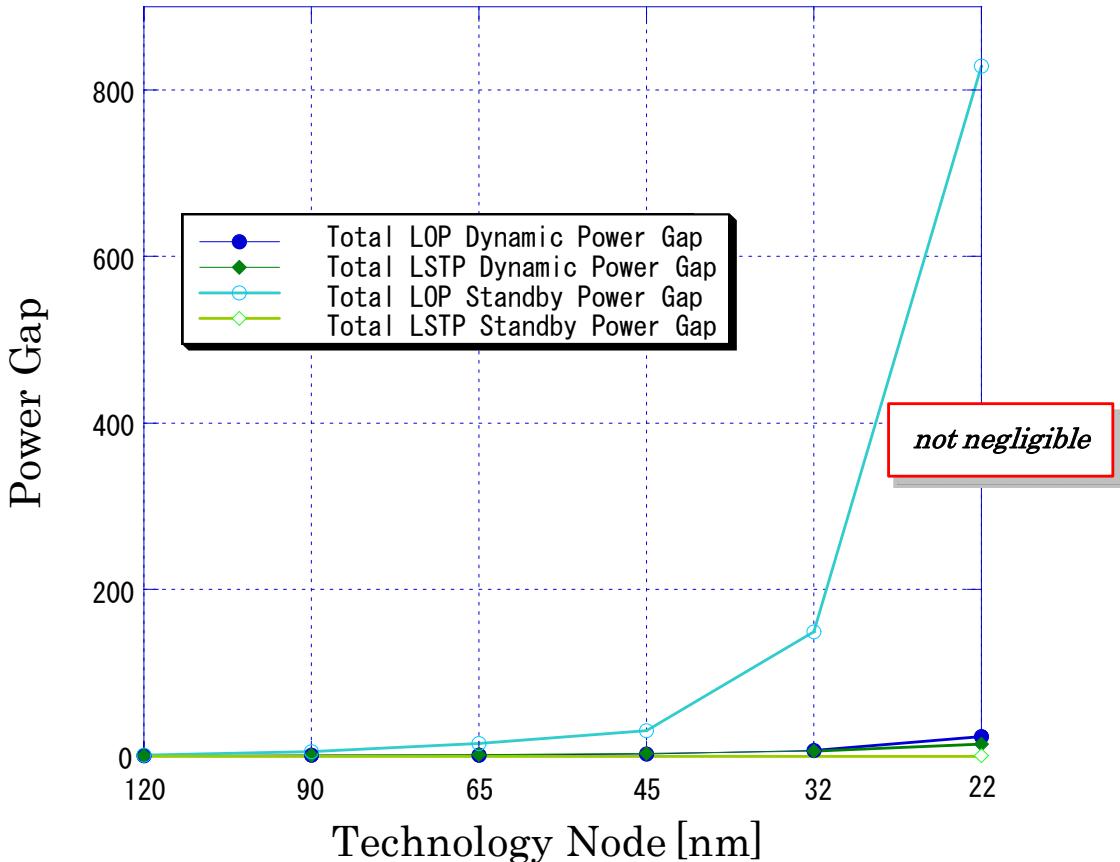

図 1-4 LOP 及び LSTP における消費電力要求値とのギャップ[5]

図 1-4にLOP及びLSTP(低保持電力仕様)における消費電力の要求値と予測値のギャップを表した図を示す[5]. 横軸がTechnology Node, 縦軸が消費電力ギャップである. この消費電力ギャップは、携帯機器用SoCに要求される一般的な消費電力指標である、動作時 0.1W(動作時), 2mW(スタンバイ時)比で定義される. 図 1-4によると 120nm プロセスまでは仕様を満たしていたもの、微細化が進むにつれて、LOPにおけるスタンバイ時消費電力が劇的に増加していくことが予測されている. この主原因として、図 1-2で示してきた広大なメモリ領域における、トランジスタからのリーク電力が挙げられる. この為、LOPに代わり、不揮発性メモリを用いたLSTPへの仕様変更が行われている.

## 1-2 相変化不揮発性メモリの位置づけ

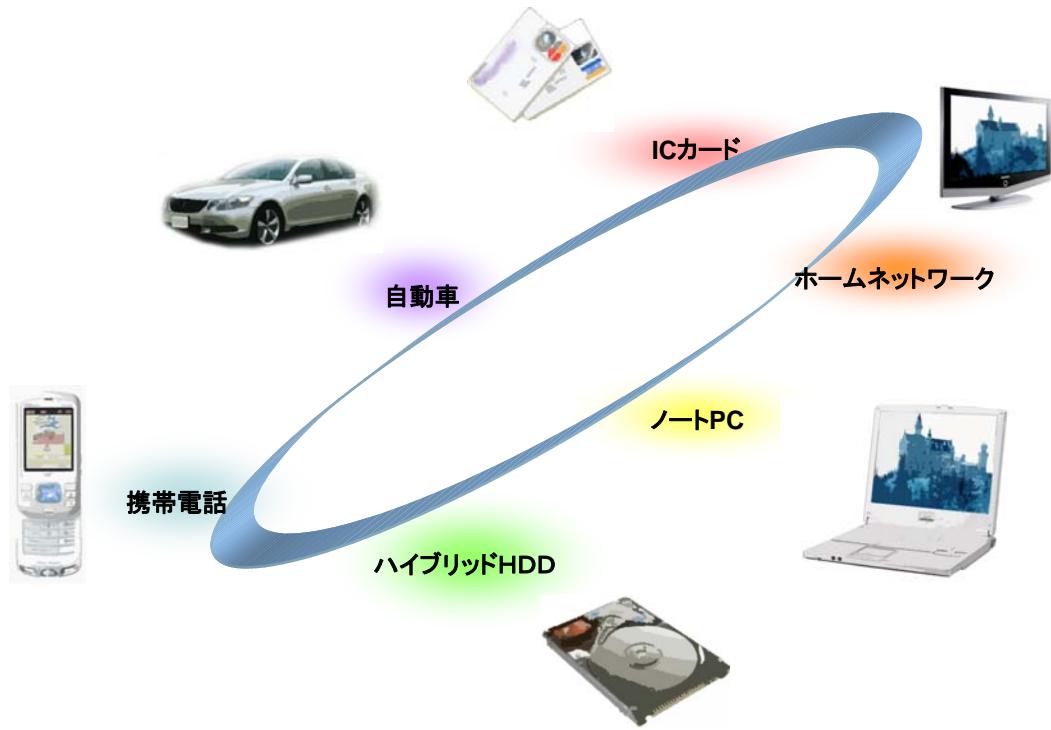

図 1-5 不揮発性メモリの応用分野例

前節で携帯機器、つまり、混載メモリ分野における不揮発性メモリの需要について述べた。不揮発性メモリは、図 1-5の応用例に示すように、高速、大容量不揮発性メモリ、インスタントオンアプリケーション、SoC、MCU(Micro Controller Unit)混載メモリの低消費電力化、プログラマブルデバイスへの応用等、様々な分野で期待が高まっている。しかし、不揮発性メモリと呼ばれるメモリは多々存在し、全ての要求を満たす唯一のメモリ(ユニバーサルメモリ)の実現は難しいと言う見方が強く、各メモリの特色によって応用用途が分かれ、住み分けされると見られている。

代表的な不揮発性メモリとしては、フラッシュメモリ(NAND型、NOR型)、FeRAM(強誘電体メモリ: Ferroelectric RAM)、MRAM(磁気抵抗メモリ: Magnetoresistive RAM)、ReRAM(電界誘起抵抗変化メモリ: Resistive RAM)、そして、本論文で取り扱う相変化型不揮発性メモリである PRAM (Phase Change RAM) が挙げられる。この相変化不揮発性メモリは OUM(Ovonic Unified Memory)や PCRAM(Phase Change RAM)、または CRAM(Chalcogenide RAM)等呼ばれているが、本論文では PRAM に統一する。

表 1-1 メモリの性能比較

| パラメータ       | DRAM[6]      | SRAM[7] | Flash[8]                               | NOR[10]                                 | FeRAM[11]                                    | MRAM[12]                                 | PRAM[14]                                      | ReRAM[15]                              |

|-------------|--------------|---------|----------------------------------------|-----------------------------------------|----------------------------------------------|------------------------------------------|-----------------------------------------------|----------------------------------------|

| 不揮発性        | ×            | ×       | ○                                      | ○                                       | ○                                            | ○                                        | ○                                             | ○                                      |

| ランダム・アクセス性  | ○            | ○       | ×                                      | ○                                       | ○                                            | ○                                        | ○                                             | ○                                      |

| 書き換え回数      | 無制限          | 無制限     | 10 <sup>5</sup> [9]                    | 10 <sup>5</sup> [9]                     | 無制限                                          | 無制限                                      | 1.0 <sup>12</sup>                             |                                        |

| 読み出し時間      | 1.6Gbps      | 3GHz    | 25us[9]                                | 400M                                    | 200M                                         | 500MHz[13]                               | 266M                                          |                                        |

| 書き込み時間      | 1.6Gbps      | 3GHz    | 250us[9]<br>(消去 2ms)                   | 2.25M                                   | 200M                                         | 200MHz[13]                               | 4.64M                                         |                                        |

| 容量[bit]     | 512M         | 70M     | 32G                                    | 1G                                      | 64M                                          | 16M                                      | 512M                                          |                                        |

| スケーリング限界要因  | トランジ<br>スタ面積 | セル面積    | セル間干渉                                  | 駆動電圧                                    | キャパシタ                                        | 電流密度                                     | リソグラフィ                                        | リソグラフィ                                 |

| 書き込み用いる物理現象 | 電荷           | 電荷      | 電荷トランジ<br>スタ                           | 電荷トランジ<br>スタ                            | 分極反転                                         | 磁化反転                                     | 相転移                                           | 電界誘起抵抗                                 |

| 研究機関        |              |         | Samsung<br>東芝<br>ST<br>Hynix<br>Micron | Intel<br>Spansion<br>シャープ<br>富士通<br>NEC | TI<br>Samsung<br>Infineon<br>松下<br>富士通<br>東芝 | IBM<br>Freescale<br>Samsung<br>ST<br>NEC | Intel<br>Samsung<br>ST<br>日立<br>エルピーダ<br>ルネサス | Samsung<br>シャープ<br>富士通<br>NTT<br>Intel |

| 特色          | DDR3         | 高速性     | 大容量                                    | 大容量                                     | 低消費電力                                        | 高速性                                      | 大容量<br>書き換え回数                                 | 動作について不明な点が多い、                         |

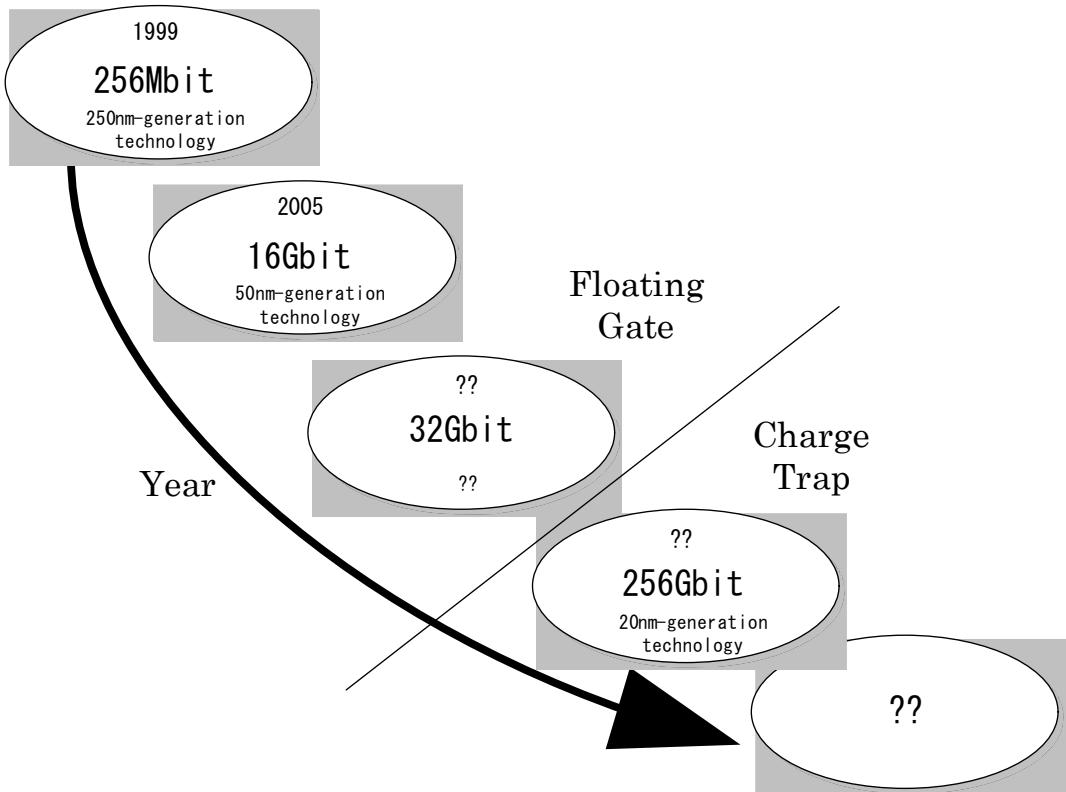

図 1-6 フラッシュメモリ(NAND型)におけるスケーリングの歴史と限界[8]

各種メモリにおける特色を表 1-1に示す。現在、次世代不揮発性メモリの用途としては、主にストレージ用途として、単体メモリ及び、MCU等の混載メモリとして開発が進んでいる。しかし、既存のキャッシュの代替としての用途までは至っていない。表中の特色の項でも触れたが、RFID等、低消費電力で動作させる環境においてはFeRAMが代表される。主に車載等、高速性、及び書き込み消去が頻繁に行われる環境においてはMRAMが代表される。ここで、本論文で扱うPRAMの用途としては大容量なストレージ用途と、高いCMOS技術との親和性から混載向けに適している。これはそれぞれ現市場ではフラッシュメモリが代表している。ストレージ用途としてのフラッシュメモリは、ビットコストを低減させる多値化技術を確立し、コストパフォーマンスで他の不揮発性メモリに群を抜いている。図 1-6にフラッシュメモリ(NAND型)のスケーリングの歴史を示す。図に示すように良好に容量を増やしてきたが、フラッシュメモリの欠点として動作速度が遅いことと、特に 50nm加工プロセス付近でのスケーリング限界が存在していた。そこで、このフラッシュ代替を目的として、PRAMが有力視されている。PRAMは多値技術を備え、動作速度も良好であり、記憶素子の読み出しマージンが広く、さらにその単純な構成からスケーリ

ングにも秀でており、スケーリング限界は 10nm以下とされている。しかし、フラッシュメモリも従来の”Floating Gate”技術から”Charge Trap”技術を導入し、20nm加工プロセスへの見通しを得た[8]。大容量化に関しては今後も激しい性能競争になると思われる。混載用途としてのフラッシュメモリとの比較については、製造に独自の生産ラインに載せなければならず、メモリコアIPとして組み込まなければならないフラッシュメモリに比べ、PRAMは配線層プロセスで、従来の製造工程に追加して実装することが出来るために、実装するコストを抑えられるだけではなく、設計の段階でスタンダードセルとして組み込める可能性もあり、真の意味での混載を実現することが可能であると有望視されている。

最後に ReRAM について述べる。ReRAM は金属酸化物材料を記憶材料とする ReRAM は 2000 年、米 IBM により初めて記憶素子材料の物性が発表された。その後、2002 年にシャープからペロブスカイト型金属酸化物による 64 ビットの ReRAM(当時は RRAM) が発表されたが、その材料の動作原理についてはほぼ未知であった。

最後に ReRAM について述べる。ReRAM は金属酸化物材料を記憶材料とする不揮発性メモリである。ReRAM は 2000 年、米 IBM により初めて記憶素子材料の物性が発表された。その後、2002 年にシャープからペロブスカイト型金属酸化物による 64 ビットの ReRAM(当時は RRAM) が発表されたが、その材料の動作原理についてはほぼ未知であった。しかし、その物性から、フラッシュに対抗できるいくつもの長所(抵抗のスイッチング時間が 100ns、クロス・ポイント構造のセル面積が最小  $4 F^2$  :  $F$  は設計ルール、抵抗変化率が大きく多値化が可能) を備えており、大変注目されているメモリである。この物性は幾つかの現象が重畳して実現されていると討論されていたが、近年、多くの研究グループが共通見解に至った。未だ動作原理の完全な解明に至っては居ないが、金属酸化材料の違いによって“接合界面型”と“フィラメント型”的 2 種類に収束した。

#### “接合界面型”

金属酸化物と電極の接合界面で抵抗変化が生じるのは、主に  $\text{PrCaMnO}(\text{PCMO})$  や  $\text{Nb}$  添加  $\text{SrTiO}$  といったペロブスカイト型金属酸化物を使う記憶素子である。この材料を使う素子は、印加電圧の極性を反転させると抵抗値が大きく変化する「バイポーラ型」の特性を示す。その後、素材によって接合界面での抵抗値変化の機構が異なる。

#### “フィラメント型”

フィラメントで抵抗変化を生じるのは  $\text{NiO}$  や  $\text{TiO}_2$  といった二元系金属酸化物を使う記憶素子である。この記憶素子は印加電圧の極性によらず、電圧の絶対値の違いで抵抗値が変化する「ノンポーラ型」の特性を示す。その後、素材によって接合界面での抵抗値変化の機構が異なる。

詳細は文献[15]をご参照して欲しい。

### 1-3 研究動向

この節では、現在 PRAM に関する企業・研究機関の研究動向について触れる。

#### 1-3-1 開発企業

現状では、図 1-7 に示すような企業が PRAM の開発に乗り出している[16]。世界半導体ランクイング上位の大手半導体メーカーがフラッシュメモリの後を継ぐ不揮発性メモリとして最有力視しているのが PRAM である。例えば、Samsung は、FeRAM, MRAM, OxRRAM など多くの新型メモリを開発しているが、PRAM に最も高い優先順位を付けている。ここに来て、エルピーダメモリ[17]、米 IBM Corp、独 Infineon Technologies AG、台湾の大手メモリメーカーである Macronix International 社が PRAM の開発に名乗りを挙げた。他の新型メモリ(MRAM, FeRAM)の開発では、撤退する企業がある中、PRAM の開発においては、さらに大手が開発に名乗りを挙げていることで注目が集まっている。PRAM に注目が集まりだした理由の一つとして、22nm の設計ルールでも微細化できることが出来ること。フラッシュメモリと比べると、セルへのデータ書き込みの時間が 1/500 と短く、かつ書き込み時の消費電力が 1/2 未満であると言われていること[23]。こうした特性を、少なくとも 22nm 世代の半導体技術まで維持できるメドが立っている[22] ということである。さらに、セルにトランジスタを使わずに作成可能[24] であることが、更なるスケーリングの可能性を強めている。

| アジア                                                                                                                    | 米国                               | 欧州                         |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|

| 韓国 Samsung Electronics Co Ltd                                                                                          |                                  |                            |

| 台湾 Macronix International Co Ltd                                                                                       | 3社が PRAM 開発で技術提携                 | 独 Infineon Technologies AG |

| 4社が PRAM を共同開発                                                                                                         | 米 Intel Corp                     | 伊仏 STMicroelectronics 社    |

| 台湾 Powerchip Semiconductor Corp<br>台湾 Nanya Technology Corp<br>台湾 Winbond Electronics Corp<br>台湾 ProMOS Technologies 社 | 日本                               | 日立製作所とルネサステクノロジ            |

|                                                                                                                        | PRAM 技術を DRAM 開発に活用<br>エルピーダ メモリ |                            |

図 1-7 PRAM 開発企業[16]

#### 1-3-2 チップ集積化報告

集積化の報告は、表 1-2にまとめる。Intel社はOUMと名前を変え 4Mbitのテストチップを報告している[18]。対して、BAE社のWeb pageにおいても同容量である、4Mbitチップの作成報告[19]が掲載されている。一方STmicroも同様に 4Mbitのテストチップ[20]を試作している。ここにきて、Samsungはこれまでに報告されたどのPRAMよりもセル面積において最小な  $0.0467\text{um}^2$ を実現し、512Mbitの容量のチップを報告した[14]。時を同じくして、IBMとMacronix International社、Qimonda AG社の 3 社が協同で試作した新しいセル構造も報告されている[21]。この報告では 22nmプロセス、セルサイズ  $0.006\text{um}^2$ の目処を示し、45nmプロセスに壁があるフラッシュメモリに 2 世代は差を付けることが出来るとした。また、ルネサステクノロジ社と日立製作所は、共同で 1.5Vの低電圧に対応したチップの開発した[22]。さらに、このチップでは下位電極と相変化材料との間に、熱比率の高いTa<sub>2</sub>O<sub>5</sub>膜を挟むことで、熱の効率的に利用し、発熱を安定させ、結果、書き込みのバラツキを低減させることに成功している。

相変化メモリでは、連続的な読み出し動作により記録膜が発熱し、書込まれた記憶データが失われてしまうという課題があったが、読み出し時にメモリセルへのアクセスを行わず、別個設けたバッファからデータを読み出す回路技術“実効アクセス回数低減方式”を開発し、読み出し寿命を 500 倍に改善した。GeSbTe 膜の粒径を小さくすることでデータ保持特性も向上し、これまで PRAM では 75°C 前後だった 10 年間のデータ補償温度を、100°C に高めることができた。また、128kB 容量のメモリモジュール面積が、従来の混載不揮発メモリに比べ 3 分の 2 以下となる見込みが得られている。実用化レベルの報告がここ数年出てきている世の中に出回るのも時間の問題だと思われる。

表 1-2 報告されている集積化されたメモリの仕様

| 研究機関                   | Intel[18]                       | BAE[19]<br>[20]       | ST micro<br>(2k x 2k) | Samsung[14]          | IBM[21]                                        | 日立製作所[22]<br>ルネサステクノロジ                                         |

|------------------------|---------------------------------|-----------------------|-----------------------|----------------------|------------------------------------------------|----------------------------------------------------------------|

| メモリ容量                  | 4Mb<br>(256k x 16)              | 4Mb<br>(512k x 8)     | 4Mb<br>(2k x 2k)      | 512Mb                |                                                |                                                                |

| デザインセル[um]             | 0.18                            | 0.25                  | 0.18                  | 0.09                 |                                                |                                                                |

| 電源電圧[V]                | 3.8                             | 3.8                   | 3.0                   | 1.8                  |                                                | 0.18                                                           |

| リード/セット/<br>リセット時間[ns] |                                 | 70ns/<br>500ns(write) | 45/150/40             | 4.64M<br>ペイト/秒       |                                                |                                                                |

| 消費電流                   |                                 | 15mA                  | 30mA                  |                      |                                                |                                                                |

| メモリセル                  | GeSbTe<br>+ Bipolar             | GeSbTe<br>+ NMOS      | GeSbTe<br>+ NMOS      | GeSbTe               |                                                |                                                                |

| メモリセルサイズ               | 0.249um <sup>2</sup><br>(7.7F2) |                       | 0.0467um <sup>2</sup> | 0.006um <sup>2</sup> |                                                |                                                                |

| その他                    |                                 |                       |                       | に目処                  | 及び、<br>Macronix<br>International<br>Qimonda AG | リセット電流100uA<br>Ta <sub>2</sub> O <sub>5</sub> 膜を使用し、<br>バラツキ低減 |

### 1-3-3 大容量化に関して

PRAMにおいては、22nmプロセスにおいても、スケーリングが可能であると報告されていること[21]や、最終的にはアクセスにトランジスタの必要性さえないと言われていること[24]から、大容量な記憶メモリ用途として用いることが出来る。また、PRAMは素子を用いて記憶するものであり、制御をすることでその素子の状態を複数つくりだすことが可能なため多値記憶ができる可能性を持っている。多値化によってビット/コストの削減が可能であり、より高密度で大容量のメモリの開発が期待できる。大容量化には、

1. 素子の微細化(高集積化)

2. 多値化

3. 素子の3次元化

の方法が挙げられる。

#### 1. 素子の微細化(高集積化)

素子の微細化はリセット電流の削減にも効果があり、多くの報告がなされている。PRAMは熱によって書き込み消去を行っているので実際に書き込み行うセルの隣接しているセルまでもが加熱され、書き換わる懸念があるが、スケーリングについては22nmまで物理的な問題がないことをIntelから報告[12]されている。

#### 2. 多値化

多値化に関する報告を表1-3 提案されている多値記憶方法にまとめる。Ovonyx,incでは、リセット電流値を可変とすることによって、素子抵抗を段階的に可変とすることに成功している。文献では、16段階(4bit/cell)の多値化が紹介されている。[22]金沢大学では、セットパルスの回数によって素子抵抗を段階的に可変することに成功している。金沢大学では、8段階(3bit/cell)に素子抵抗が可変とできることを確認している[23]。相変化メモリは、抵抗の大小を論理値の0と1で記録するが、この約2オーダーの抵抗変化がある。この大きな抵抗変化を段階的に変化させることによって多値化を行うのが以上の方法である。

抵抗値を段階的に可変とする以外の多値化の方法も提案されている。ECD社から提案されている方法[24]は、結晶化時間を利用している。結晶化には、決まった時間が必要である。通常のセット動作では、決まった時間以上のパルスを印加するが、印加パルス幅を決まった時間より短いものとする。すると、結晶化には複数回のパルス印加が必要になる。例えば、結晶化に10回のパルス印加が必要になるようにパルス幅を設定しておく。ある素子にあらかじめ3回パルスを印加しておけ

ば、残り 7 回別途パルスを印加すると結晶化する。この別途印加が必要なパルス回数をカウントすることによって多値化が可能である。また松下電器産業では、結晶化温度と結晶化時間の異なる材料を重ねることによって多値化を行う方法[25]を提案している。

### 3. 素子の3次元化

大容量化には、多層化も考えられるが実施例は、まだ報告されていない。

表 1-3 提案されている多値記憶方法

| 研究機関   | 多値段階      | 素子材料                                            | 多値化手法      | 詳細                                                                     | 備考                                     |

|--------|-----------|-------------------------------------------------|------------|------------------------------------------------------------------------|----------------------------------------|

| Ovonyx | 4bit/cell | Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> | 電流パルスの電流量  | リセット電流値を可変にすることで素子抵抗値を段階的に可変にしている。                                     | 書き込み時間 ○<br>集積性 ×<br>安定性 △<br>制御しやすさ ○ |

| 金沢大学   | 3bit/cell | Se <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> | 電流パルス回数    | 複数回セットパルスを印加することで素子抵抗値を段階的に可変にしている。                                    | 書き込み時間 ×<br>集積性 ○<br>安定性 ○<br>制御しやすさ ○ |

| ECD    | 3bit/cell |                                                 | 結晶化時間      | 結晶化時間を満たすパルスをあらかじめ複数回のパルス印加にわける。まず最初にパルスをあたえ、残りのパルスの印加回数をカウントして多値化を行う。 | 書き込み時間 ○<br>集積性 △<br>安定性 ×<br>制御しやすさ △ |

| 松下電器産業 | 2bit/cell |                                                 | 結晶化材料数を増やす | 結晶化温度と結晶化時間の異なる材料を重ね合わせることで多値化を行う。                                     | 書き込み時間 ○<br>集積性 ○<br>安定性 ×<br>制御しやすさ × |

### 1-3-4 低消費電力に関して

リセット電流削減方法とその効果について述べる。提案されている主なリセット電流削減方法は、

1. 相変化部の体積削減

2. 低融点の相変化材料の使用

3. 結晶状態の抵抗値の増加

4. 電極材料の最適化

である。

#### 1. 相変化部の体積削減

1970 年代に 100mA 以上必要だったもの[25]が、2000 年以降には、数 mA へと削減された。これは、主に素子の微細化によるところが大きい。素子の微細化しても低効率の変化を利用する相変化メモリは、問題がない。よって微細化に向いている。微細化により書き込み電流が容易に削減できる[17][26]。さらに Samsung が提案するエッジコンタクト[27]を利用することにより、微細化が大幅に進み、1mA 未満のリセット動作が可能となる。エッジコンタクトを利用する方法は、相変化部と電極との接触面に電極(配線)層の膜圧方向を利用する構造になっている。この構造では、接触面積が最小設計寸法(F)より微細化できるという特徴を持つ。このエッジコンタクトを利用した方法は、製造技術の進展を待たずして微細化が可能であるため、有効な手段といえる。STmicro は u-トレ

チ法を用いて、堆積を減らす方法を提案している。[28]

## 2. 低融点の相変化材料の使用

低電流でリセット動作可能な相変化の探求[29][30]も試みられている。例えば、低融点の相変化材料を使用する金沢大学の試みでは 10mA以上必要としているが、これは素子サイズが大きいためであり、コンタクト面積当たりの電流値は、Intel, Ovonyxなどの値から 4 分の 1 の  $20\text{mA}/\mu\text{m}^2$ 程度まで削減することが可能である。[30]

## 3. 結晶状態の抵抗値の増加

Samsung は窒素(N)を GeSbTe 系材料にドープし結晶状態の抵抗値を上げている。これにより窒素をドープしていないものに比べ、リセット電流を半分以下(40%)に削減することに成功している[31][32]。また日立製作所は、酸素(O)を GeSbTe 系材料にドープし、リセット電流を  $100\mu\text{A}$  に抑えることに成功した。[33][34]

## 4. 電極材料の最適化

注目すべきは、日立製作所から発表された加熱用ヒーター材料にタンゲステン(W)を用いた素子[35]である。メモリセル構造は Intel などと同じボトムコンタクトを利用しながらも必要なリセット電流を  $50\mu\text{A}$  ( $0.16\mu\text{m} \times 0.16\mu\text{m}$ ) に抑えた。リセット電流が  $50\mu\text{A}$  に抑えられたことにより、選択用トランジスタのゲート幅は  $0.1\mu\text{m}$  で済むと報告されている(トランジスタの駆動電流がゲート幅当たり  $500\mu\text{A}/\mu\text{m}$  と仮定)。リセット電流が削減できたのは、素子の微細化以外にタンゲステンを電極として使用したことが大きいようである。タンゲステンの格子間隔( $a=0.316\text{nm}$ )の 2 倍( $0.632\text{nm}=0.316\text{nm} \times 2$ )が、GeSbTe 系の場合( $a=0.601\text{nm}$ )とほぼ一致している。他の報告では、TiN(格子間隔  $a=0.425\text{nm}$ )などが電極に使用されている。タンゲステン電極を用いると、電極材料と相変化材料の格子間隔が似ていることから電極層と相変化層の界面がスムーズとなり、これがリセット電流削減の要因の一つと推測される。その他にも Samsung は、相変化材料の間に電極を挟む方法[36]や加熱用ヒーター電極に TiN を用いる方法[31][32]を提案している。

## 1-4 目的

本研究は、前述した背景のもと、相変化不揮発性素材を用いたメモリアーキテクチャを、3つの観点から提案し、実現することを目的とし、行った。以下にその内容を示す。

- ここでは CMOS0.35um プロセスを用いて、相変化不揮発性メモリの記憶材料であるカルコゲナイト半導体の電気的特性評価回路を作成。得られた特性から、回路に必要なパラメータを抽出。さらに幾つかのカルコゲナイト半導体デバイスパラメータを用いてシミュレーションモデル構築。

- CMOS プロセス上で実装するための基礎研究と低消費電力化。評価で得られたパラメータから、CMOS0.35um プロセスを用いて、相変化不揮発性メモリアーキテクチャを考案。さらに、書き込み電流低減手法及びアーキテクチャを提案。

- テクノロジノード 45nm 以下、混載メモリにおけるフラッシュメモリ代替を目的とした多值回路。大容量化の観点から、独自の多值記憶手法によって得られた実験結果を基に、多值化相変化不揮発性メモリアーキテクチャを考案。

- PRAM の動作速度、リテンションタイム及び SRAM の静的消費電力の改善を目的とした新しいセルアーキテクチャを考案、SRAM、PRAM 双方の欠点を改善し、CMOS0.18um プロセスを用いて、設計に至る。

## 1 – 5 本論文の構成

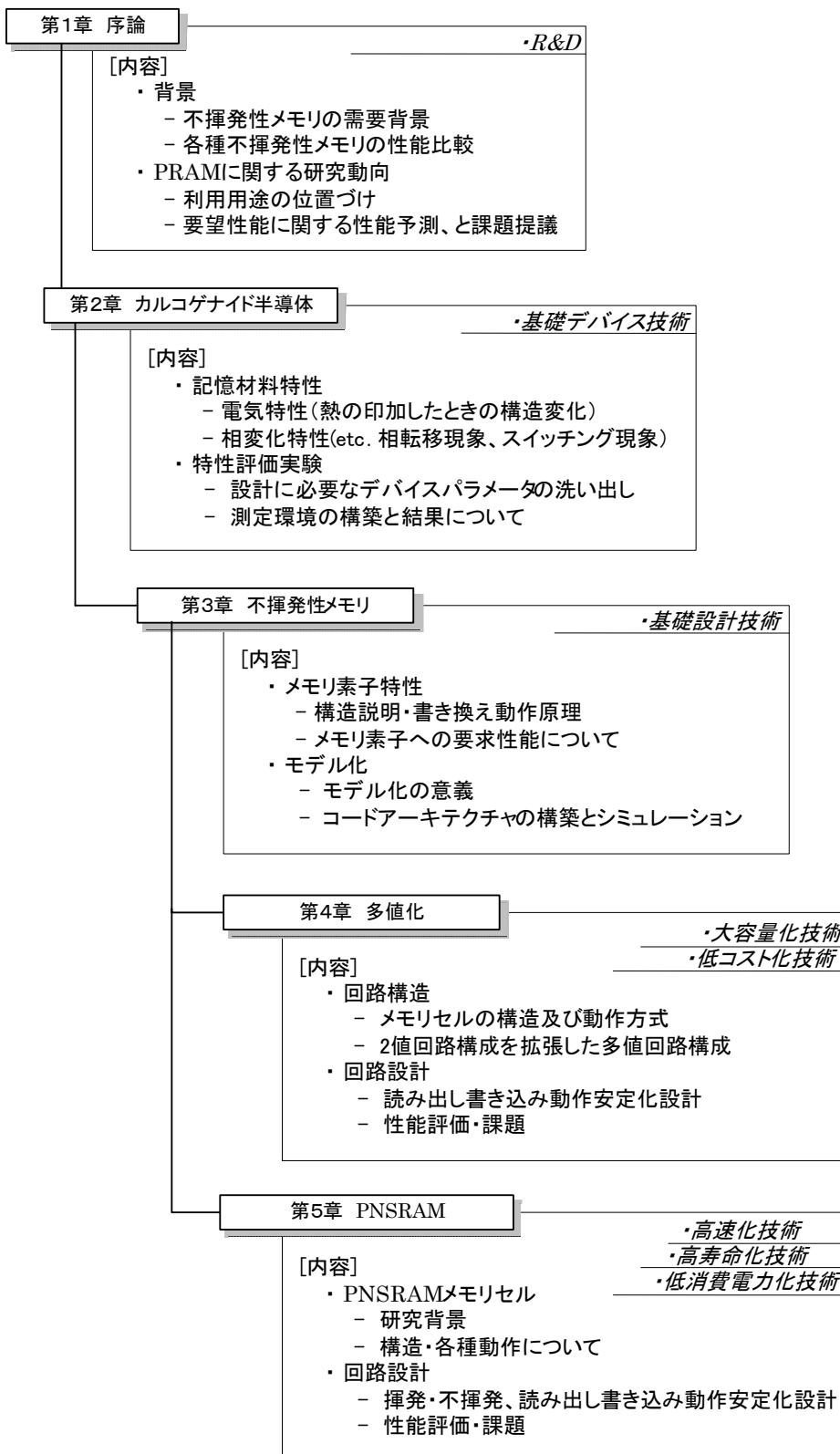

本論文は前述の目的を達成する為に, CMOS 混載相変化不揮発性メモリの実用化を成し得るための実験手法, 設計手法, 及び高性能を図るための回路アーキテクチャに関する研究成果をまとめたものである. 本論文の構成と各研究の概略について以下に記述する.

### 第1章 序論

本研究は相変化不揮発性メモリのアーキテクチャ・設計手法に関し, 目的別に幾つかのアプローチを試みている. ここでは, 各章に共通する技術的背景及び, 本メモリにおける近年の研究動向について記述する.

### 第2章 カルコゲナイト半導体

この章では, 相変化不揮発性メモリの記憶材料であるカルコゲナイト半導体の物性について述べる. 特に, カルコゲナイト半導体材料はDVD等の光ディスクへ幅広く応用されているだけに研究も深いが, ここでは, CMOS 回路への実装を基に必要な物性について記載する. また, 実際にカルコゲナイト半導体の物性を調べた特性評価実験の方式・環境・結果について述べる.

### 第3章 不揮発性メモリ

この章では第2章で述べた相変化不揮発性メモリをどのようにして CMOS プロセスと結びつけるかについて記載する. CMOS プロセスと組み合わされたメモリセル, その構造・書き換え手法について言及後, 相変化不揮発性メモリとして, 要求される性能と, その特性について記載する. また, 2種類のカルコゲナイト半導体シミュレーションモデルを考案した. 前者はチップ上へのカルコゲナイト半導体の蒸着に際し, そのデバイス構成・膜圧が適しているかどうかをシミュレーションする熱的モデルであり, 後者はCADによる回路シミュレーションにおいて, カルコゲナイト半導体の特性を再現するモデルである.

## 第4章 多値化

この章では、本研究室で得られた、多値化を実現する実験結果を基に、第3章で述べた相変化不揮発性メモリの基礎回路を拡張し、多値回路を実現するアーキテクチャについて記載する。最後に2値メモリとの比較を通じて、多値化の利点について纏める。

## 第5章 PNSRAM

従来の6トランジスタSRAMにとPRAM(1T2R)を組み合わせた新しい回路方式であるPNSRAMを提案し、動作検証を行った。このアーキテクチャはSRAMの静的消費電力、PRAMの動的消費電力、リテンションタイム、書き換え速度を改善する。このメモリアーキテクチャの動作及び、将来の消費電力動向について記載していく。

## 第6章 結論

本研究で得られた相変化不揮発性メモリのアーキテクチャ・設計手法に関し、その結果について総括すると共に、本メモリのみならず、相変化不揮発性メモリとしての今後の課題、及び展開について述べる。

図1-8に本論文の構成について示す。

図 1-8 本論文の構成

## 第2章 カルコゲナイト半導体

### 2-1 始めに

この章では、相変化不揮発性メモリの記憶材料であるカルコゲナイト半導体の物性について述べる。特に、カルコゲナイト半導体材料はDVD等の光ディスクへ幅広く応用されているだけに研究も深いが、ここでは、CMOS回路への実装を基に必要な特性について触れてゆく。

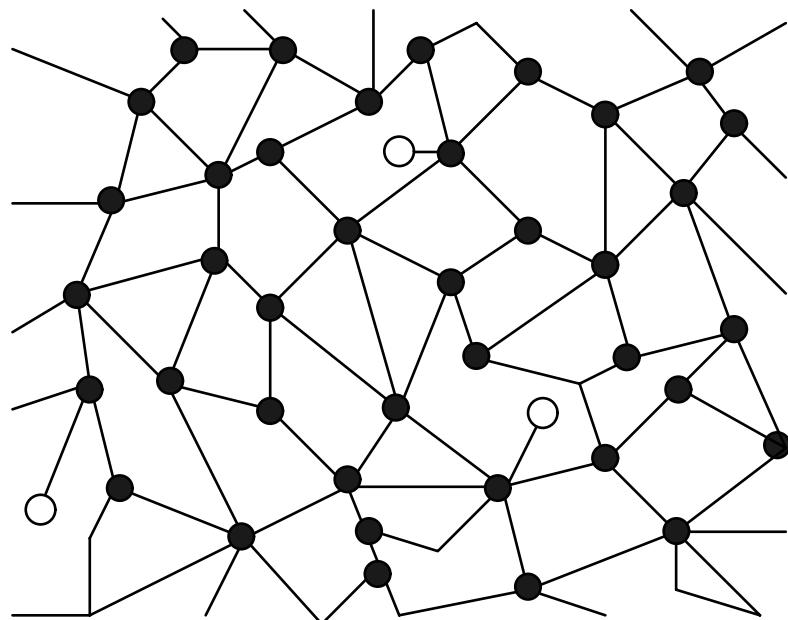

#### 2-1-1 アモルファス物質

図 2-1 アモルファス構造

アモルファスは単結晶のような長距離にわたる周期的かつ規則正しい原子配列が阻止された固体状態をいう。「アモルファス(amorphous)」という言葉は、ギリシャ語の"α-morphe"が語源であり、「はつきりとした形をもたないもの」という意味を持ち、日本語に直すと「無定型」となる。アモルファスという言葉は、固体に限定した不規則系物質を意味し、規則性をもつ結晶と対比されて使われている。身近なものではガラスもアモルファスである。

結晶は周期構造をもっており、ある特定の原子に対してその隣接原子の位置とその関係が分かれば、その関係を拡大し、すべての原子の位置を推定することができる。このことを"結晶には長距離秩序(Long Range Order: LRO)がある"という。これに対して、アモルフ

アス物質ではある原子に注目した場合に、最隣接原子同士の距離、結合角が結晶の場合とわずかに異なっている。そして注目原子から遙かに離れた原子では、秩序性が失われ、全体として捉えるとランダムである。しかし、数原子程度の距離では比較的秩序が保たれているので、アモルファス物質には長距離秩序は存在しないが短距離秩序(Short Range Order: SRO)は存在する。これらアモルファス物質の構造の典型的な模式図を図2-1に示す。このように内部には歪みが存在し、結合角の広がりや欠陥中心の生成という構造変化の結果、未結合手(ダンギングボンド)が生成されている。

このアモルファス物質は、液体あるいは気体を系全体が熱平衡に達する前に、系内の構成要素を何らかの手段で凍結して作られたものであるため、系内では局所的な熱平衡が満たされているが、それが系全体には広がっていない。そのため自由エネルギーの高い幾つかの極小値を取る、つまり非平衡準安定状態なっている。従って、熱や光等の外部からのエネルギーの供給、あるいは長時間の内部の熱運動によって、配置の組み換えが起こり、より安定な状態に系を移行させ、最終的には自由エネルギーが最小の結晶状態まで遷移させることができる。

## 2-1-2 カルコゲナイト系アモルファス半導体

相変化型不揮発性メモリは相変化材料として、カルコゲナイト半導体と呼ばれているアモルファス半導体を用いている。周期律表の第6族元素であるO、S、Se、Teは、酸素族元素または、カルコゲン(chalcogen)元素と呼ばれている。このカルコゲンとは、“銅と化合物を作る元素”という意味である。しかし、最近では、酸素(O)を除いたS、Se、Teの3元素をカルコゲン元素と呼ぶことが多い。また、これらの3元素に対しては、硫黄族元素ということもある。これらの3元素を1種、もしくは2種以上を成分とするガラス状物質を、カルコゲナイトガラス、又はカルコゲン化物ガラス等と呼んでいる。また、カルコゲナイトガラスは無機ガラスと違って、As、Geまたは、Siのような原子を含む多成分系の原子比は一定しておらず、例えば、As-S等の2成分系で原子比を異にする様々な組成が作製可能である。例えば、酸化物のAs-O系では、 $As_2O_3$ と $As_2O_5$ 組成だけが可能であるとの対称的である。そのため組成は通常、元素を成分として表される。非晶質(アモルファス)半導体としての性質を表す場合などには、カルコゲナイト系アモルファス半導体、カルコゲナイト半導体等と呼んでいる。

技術的観点からのアモルファス物質の特徴としては以下が挙げられる。

- a) 組成を連続的に変えられ諸特性を連続的に可変できるので、最適な組成が決定できる。

- b) 高度な結晶化技術が不要なため薄膜、バルクの両者とも安価に製造できる。

- c) 大面積の薄膜が容易に得られる。

- d) 構造が等方的で加工が簡単なため、量産に向いている。

このように様々な特徴を持つアモルファス物質は、学術、デバイス応用の両面から非常に関心が持たれている。多くのカルコゲン化合物が結晶-非晶質間の相変化を示すが、ある種のカルコゲン化合物は相変化が容易、非晶質状態が安定であるなど、記録媒体として優れた性質を持っている。偏析や相分離などによる劣化を考慮すると、単一元素の材料が単純であり、相変化材料として都合が良いが、必要な特性を持つ单一の元素は見つかっていない。そこで相変化材料としては多成分の化合物が使用されており、GeSbTe 系、AsSbTe 系、SeSbTe 系、AgInSbTe 系などがあげられている。GeSbTe 系、AgInSbTe 系はDVDに使用されている物質である。

## 2-2 電気的特性

### 2-2-1 電気伝導度の温度依存性

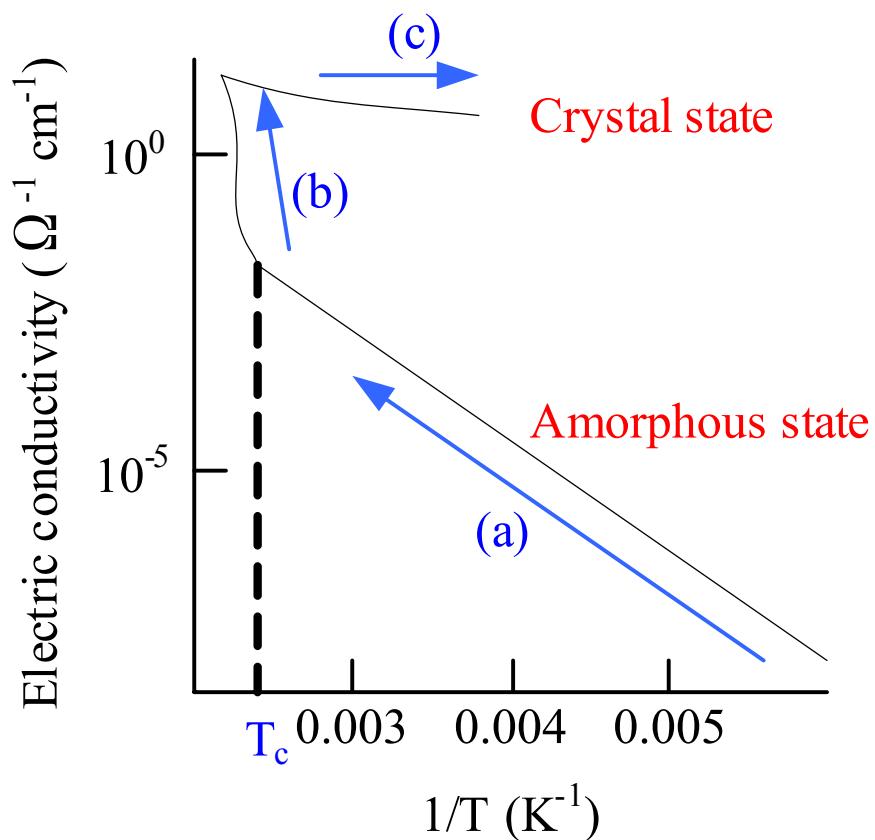

図 2-2 カルコゲナイト半導体の電気的伝導度の温度依存性

カルコゲナイト半導体薄膜の電気伝導の温度依存性を測定することによって、結晶状態及び非晶質状態の抵抗率(電気伝導度)が得られるだけでなく、結晶化温度Tcや非晶質状態の電気伝導度の活性化エネルギー等、相変化型不揮発性メモリにとって多くの重要な情報を得ることができる。

従来、バンド及びエネルギーギャップの概念は結晶半導体の解析で効果を発揮したが、その過程には長距離秩序の存在があり、長距離秩序のないアモルファス半導体には相容れないものと考えられてきた。しかし実際は、高抵抗な非晶質状態の試料を加熱すると試料の電気伝導度は式(2-1)に従い上昇する(図 2-2の(a))。

$$\sigma = \sigma_0 \exp \left( -\frac{E_a}{kT} \right) \quad (2-1)$$

ここで、 $\sigma$ は、材料固有の定数(Mottの最小金属導電率  $\sigma_{\min}$ に相当)と  $E_a$ は、活性化エネルギーであり、 $k$ はボルツマン定数を、 $T$ は絶対温度を示す。試料温度が  $T_c$ に達すると、試料は結晶化し、電気伝導度は急激に上昇する(図 2-2の(b))。結晶化した試料は非晶質状態の電気伝導特性とは違う振舞を示す(図 2-2の(c))。室温での非晶質状態の電気伝導度( $\sigma_a$ )は  $9.5 \times 10^{-4} \Omega^{-1} \text{cm}^{-1}$ 、結晶状態の電気伝導度( $\sigma_c$ )は  $13 \Omega^{-1} \text{cm}^{-1}$ であった。室温で 3 枠程度の電気伝導度比が存在する。

## 2-3 相変化特性

### 2-3-1 相転移現象

カルコゲナイト半導体(カルコゲナイトガラス)を含めたガラス物質の特徴的な性質に、ガラス転移現象や結晶化現象がある。相変化型不揮発性メモリは、これら相変化を利用してより重要な要素である。カルコゲナイトガラスを含めたガラス物質の特徴的な性質は、融点以下の温度で熱膨張係数や比熱が突然変化する温度、すなわちガラス転移温度( $T_g$ )が存在することである。これから、この転移現象について述べる。

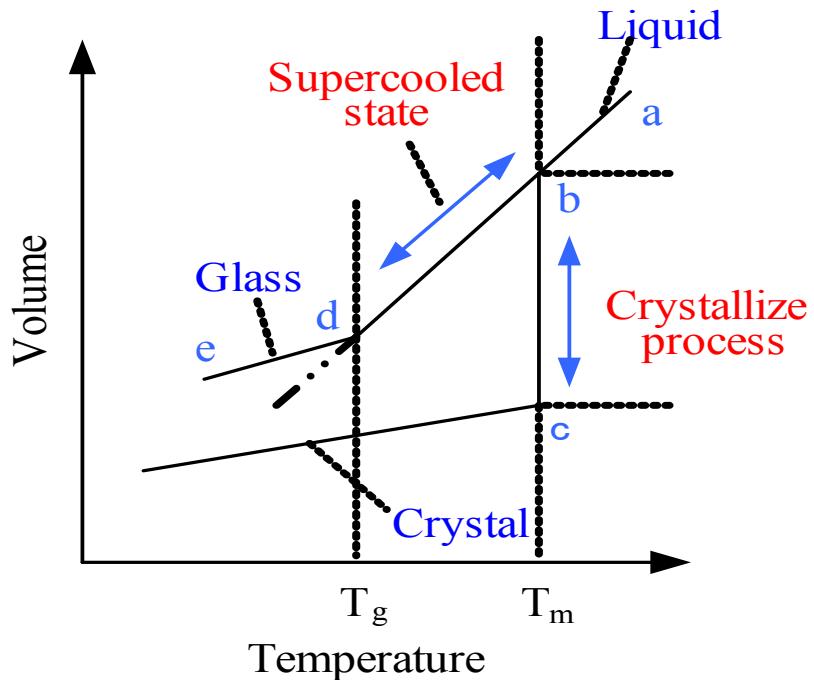

図 2-3は温度による物質の体積変化を示す。溶融(液体)状態にある試料(図 2-3のaからbの間にある状態)をゆっくり冷却すると、通常の物質ではb点で結晶固体となり、bからcへの不連続な体積変化を示す。しかし、冷却速度が早い場合やb点近傍において液体の粘度が十分に大きい物質などでは、b点に達しても結晶化がおこらず、過冷却液体となり、a → b → dに沿って体積が連続的に減少する。この状態を過冷却状態と呼ぶ。

そしてガラス転移温度 $T_g$ (図 2-3のd点)に近づくと粘度が急激に大きくなつて固化し、さらに冷却するとd → eに沿って体積が減少する。この状態がガラス状態であり、d点以下で極めて安定な固体となる。

図 2-3 カルコゲナイト半導体の体積変化

次に、eの状態からガラス状の試料を加熱していくときの状態変化を考える。eの状態(ガラス状態)の試料を加熱すると、結晶と似た膨張係数で体積が変化する。そしてガラス転移温度 $T_g$ に達すると体積の増加割合が大きくなり過冷却状態となる。過冷却状態ではガラスを構成している原子の並進運動が可能となり配列の変化が容易となる。さらに加熱して原子が拡散(移動)しやすくなると熱力学的に安定な結晶状態へ遷移する。この時の温度を結晶化温度 $T_c$ と呼ぶ。さらに加熱を続けると融点 $T_m$ で液体状態となる。

カルコゲナイト半導体は、以上のような加熱、冷却により結晶状態と非晶質状態間を遷移することができる。結晶状態と非晶質状態との間には、体積以外にも比熱、屈折率、電気伝導度等、種々の物理的特性の違いが存在する。この性質のうち電気的特性(電気伝導度)の違いを利用したものが相変化型不揮発性メモリである。なお、非晶質状態は厳密には準安定状態であり時間がたてば結晶状態へと遷移する。

### 2-3-2 相転移温度の昇温速度依存性

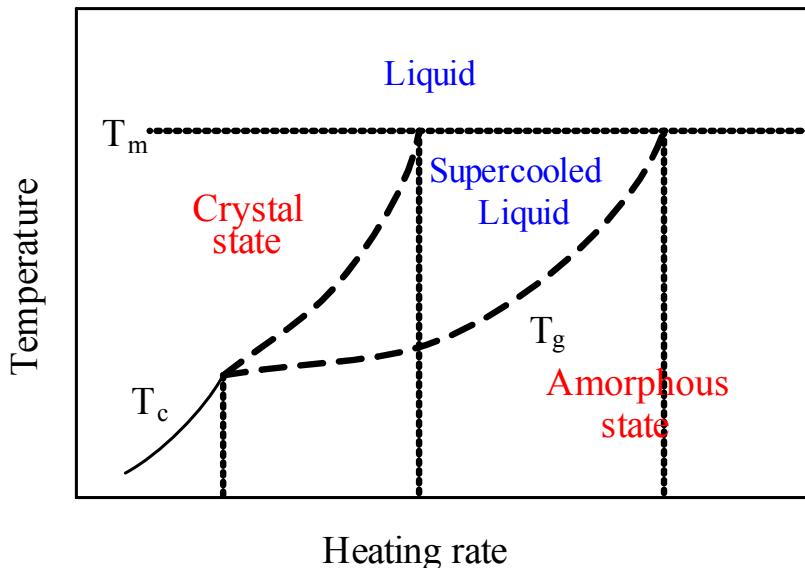

カルコゲナイト半導体の相転移においては、ガラス転移温度( $T_g$ )及び結晶化温度( $T_c$ )は昇温速度に依存することが以前から知られているが、具体的な依存関係は求まっていなかった。この関係は非晶質状態の熱的安定性、結晶化速度など、後述するメモリの特性を決める上で重要な要素となるため、この依存関係が調べられてきた。過去に得られた実験結果

を fragmentation model の適用により拡張すると、図 2-4 の Transient Phase Diagram(TPD) として表現できる。

図 2-4 TPD

図 2-4 は昇温速度により 4 領域に分割できると考えられる。

1) 第一領域：(固相－固相－液相)

低昇温速度領域であり、非晶質状態からガラス転移点を示さずに結晶化し、その後溶融する。

2) 第二領域：(固相－過冷却液体－固相－液相)

やや低い昇温速度領域であり、加熱してゆくと非晶質状態からガラス転移を経て過冷却状態となり、更に加熱すると結晶状態へと遷移し、その後溶融する。

3) 第三領域：(固相－過冷却液体－液相)

高昇温速度領域であり、非晶質状態から過冷却状態となり、その後は結晶化することなく融点に達する。

4) 第四領域：(固相－液相)

超高昇温速度領域であり、非晶質状態からガラス転移、結晶化を示すことなく溶融する。

このような TPD は広く非晶質物質の相転移に適用できると考えられる[37].

相変化の過渡応答を調べた実験結果から、昇温速度の遅い領域では、結晶化温度とガラス転移温度の差が徐々に小さくなり、結果、 $T_g$ は $T_c$ と融合してしまい、ガラス転移を示すことなく、すなわち過冷却液体を経由することなく結晶化してしまうと予想される（固相から固相への相転移）.

逆に昇温速度の速い領域では、急激に転移温度が高くなっている。さらに昇温速度が速い領域では $T_c$ は $T_m$ （融点）に達すると予想される。その結果速い昇温速度の領域では非晶質状態から過冷却液体になり、結晶化せずに液体へと転移することになると予想される。さらにより速い昇温速度領域では、 $T_g$ が融点 $T_m$ に達すると予想されるので非晶質状態から、ガラス転移や結晶化現象を示すことなく液体状態へと転移すると予想される。

### 2-3-3 スイッチング現象

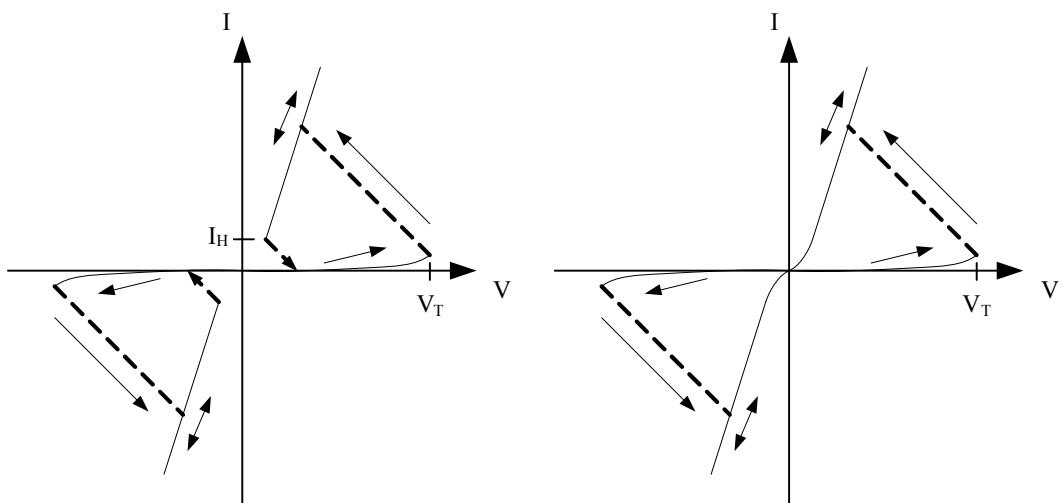

図 2-5 スイッチング現象

(a) 閾値型スイッチング現象

(b) メモリ型スイッチング現象

適当な組成のカルコゲナイト半導体薄膜を金属電極でサンドイッチ状にはさみ電圧を印加すると、図 2-5に示すような 2 種類の電圧電流(閾値型またはメモリ型) 特性を示す。Te<sub>50</sub>As<sub>30</sub>Si<sub>10</sub>Ge<sub>10</sub>のような材料は結晶化しにくく、図 2-5 (a)のような閾値型の特性を示す。この閾値型を示す材料に電圧を印加すると閾値電圧 $V_T$ で急激に低抵抗な状態に遷移する。電圧を下げて電流が $I_H$ 以下になると元の高抵抗状態に戻る。この現象を閾値型スイッチング現象と呼ぶ。図 2-5(b)のようにメモリ特性を示す試料では、高抵抗状態の試料に電圧を印加すると、閾値電圧 $V_T$ で急激に低抵抗状態に遷移し、一旦この低抵抗状態に遷移するとこの状態を保持するため、電圧を下げるても元の高抵抗な状態には戻らない。この現象

をメモリ型スイッチング現象と呼ぶ。

以上の現象を総じてスイッチング現象と呼ぶ。この現象の原因としては、膜厚が厚い場合には熱的な効果が、膜厚が薄い場合は電界効果が関与しているといわれ[38]、

スイッチング現象には、

- a) 局部的電界破壊による電流増倍に伴う温度上昇

- b) キャリア数の増化により局在準位が埋められることによる影響

等、種々の説がある。

なお、非可逆的な現象であるメモリ効果は、結晶化した低抵抗な電流パスを固定することにより行われる。すなわち、スイッチング現象で、高抵抗状態から低抵抗状態への遷移後、電極間に生じるフィラメント状の電流パス中で発生するジュール熱によって、非晶質状態から結晶状態への熱的な相転移がおき、結晶化した低抵抗な電流パスが形成されるというものである。この状態に、さらに幅の短い大電流パルスを印加すると、低抵抗状態から高抵抗状態に戻るのは、結晶化した電流パスが溶融し急冷されることによって、試料が結晶状態から非晶質状態に転移しているためである。これを利用しているが本研究のメモリである。

#### 2-3-4 発振現象

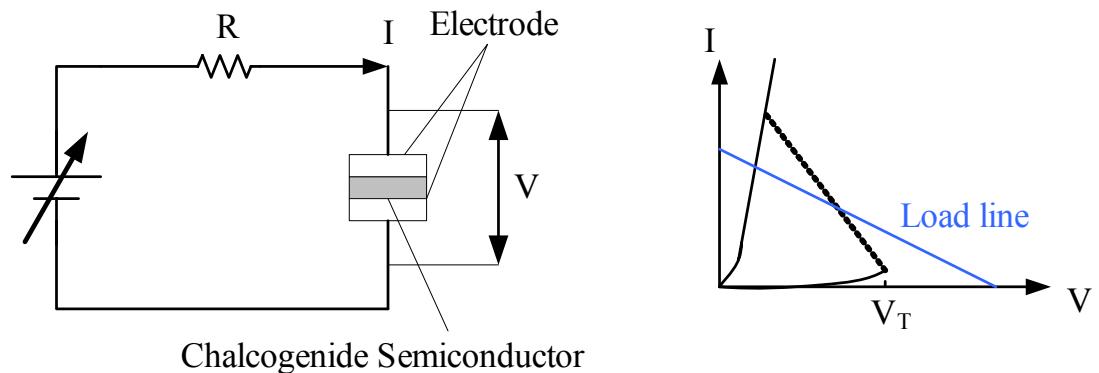

前述したように、閾値型スイッチ、メモリ型の両方とも電流電圧特性は、“S字特性”をしているため、図 2-6(a)に示すようにカルコゲナイト半導体に適当な抵抗Rを直列につなぎ電圧を印加すると、発振現象が観測される。これは、負荷線が図 2-6(b)のようにカルコゲナイト半導体の負性抵抗領域で交差する時見られる現象である。本研究で用いるメモリ型を示す材料でもこの現象がまれに観測される。

図 2-6 発振現象 直流特性

(a) 回路

(b) 直流特性

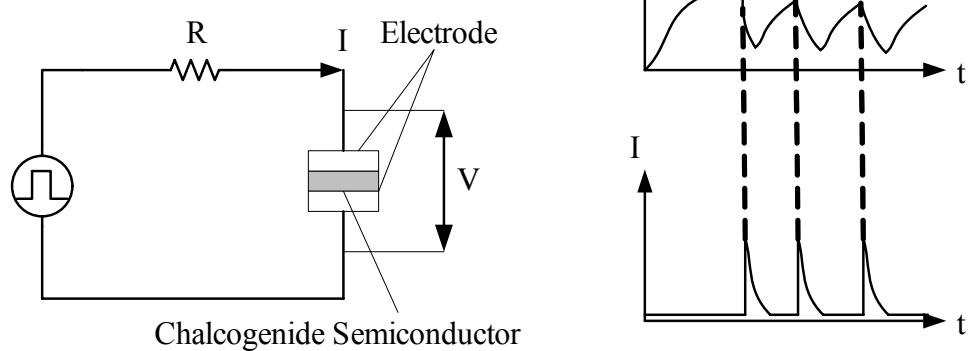

図 2-7 発振現象 過渡特性

(a) 回路

(b) 電圧電流特性

図 2-7(b)に示すように、発振現象をおこすと、試料には発振周期毎にしか電流が流れないため、試料が加熱されにくい。そのため相転移が生じない、若しくは相転移が生じにくくなる。本研究で使用したAsSbTe系材料でも稀にこの発振現象が観測された。その時の発振周波数は 300kHz 程度であり、負荷抵抗(電流制限用抵抗)が  $5k\Omega$  以上の時にしばしば観測された。このように“S 字特性”を示す負性抵抗の発振周波数は一般的に低い。低いが故に加熱されにくいとも言える。

## 2-4 モデル化

研究を進める上で、カルコゲナイト素子の特性を得ることは必須であるが、この計測を行う場合、ガラス基板上、もしくは作成したチップ上（TEG回路により計測）にカルコゲナイト素子及び、必要な電極を作成する必要がある。しかしながら、この行程は時間的及びコストの面から、安易に実験を進めるのは無駄が多い。そこで、研究を進める上で2種のカルコゲナイト素子のシミュレーションモデルを作成した。この詳細については、後日、論文として纏め発表する。

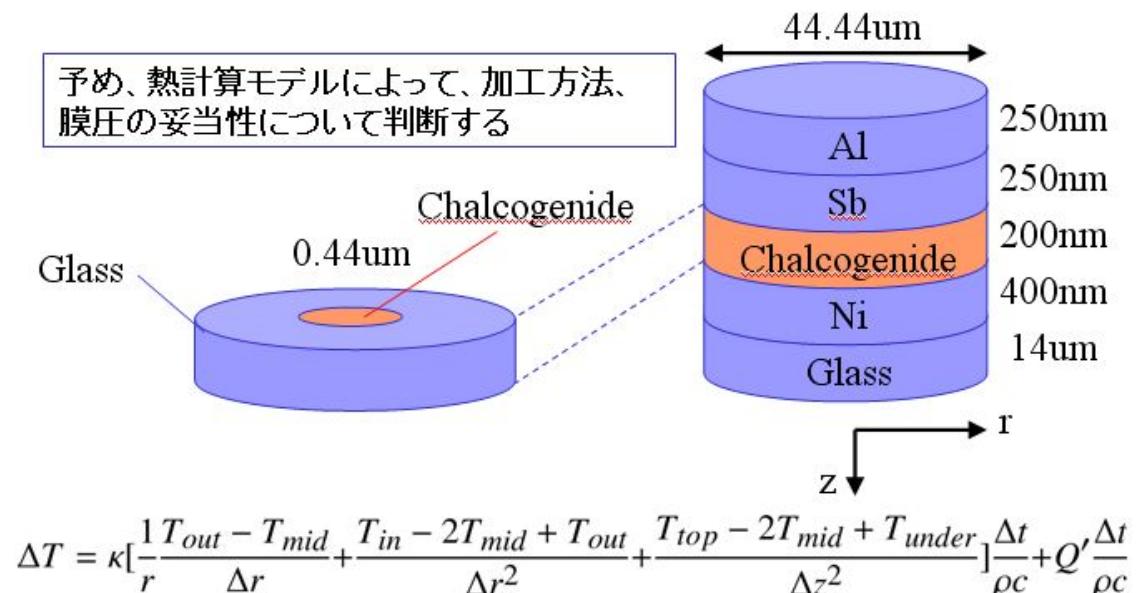

図 2-8 詳細熱計算モデル

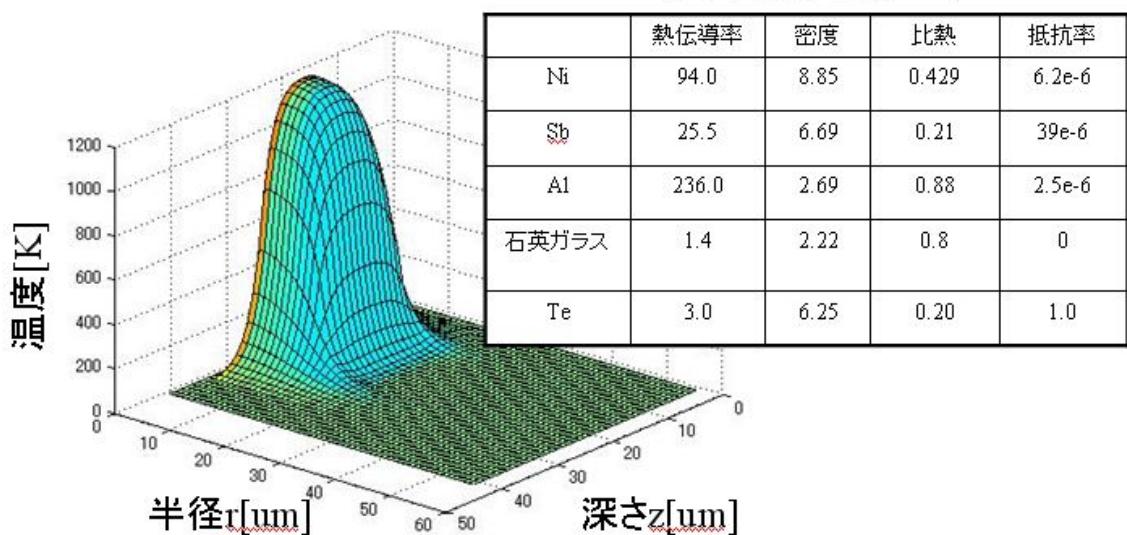

一つはメモリセルを構成する物質の熱容量等のデバイスパラメータを用いて熱方程式を解く詳細熱モデルである。その計算式と、ガラス基板上での動作を模倣したモデルを図2-8に示す。このモデルを用いることでメモリセル構造を実際に作成する前に、その構造における熱分布を模擬し評価することが可能となった。このMATLABを用いたシミュレーション結果及び、使用したデバイスパラメータを図2-9に示す。このシミュレーションでは10μsecの間、1mAをカルコゲナイト半導体(SeSbTe)へ加えた結果である。なお、このシミュレーションでは、図2-8中カルコゲナイト半導体フィラメントにはTeが支配的としてその熱伝導率を用いて行った。

■ T=1.0e-8[sec]、1mA

### デバイスパラメータ

図 2-9 詳細熱計算モデルシミュレーション結果

図 2-10 簡易熱計算モデル構造

また、もう一方のモデルがCADを用いて、メモリ回路設計を行う場合に用いる簡易熱計算モデルである。2章で示したように、記録材料であるカルコゲナイト半導体は極めて複雑な特性を持っている。一般的に回路検証時において、相変化素子は抵抗モデルに置き換えられるが、素子変化による回路への影響が判別しづらい。そこで今回のモデル作成に至った。

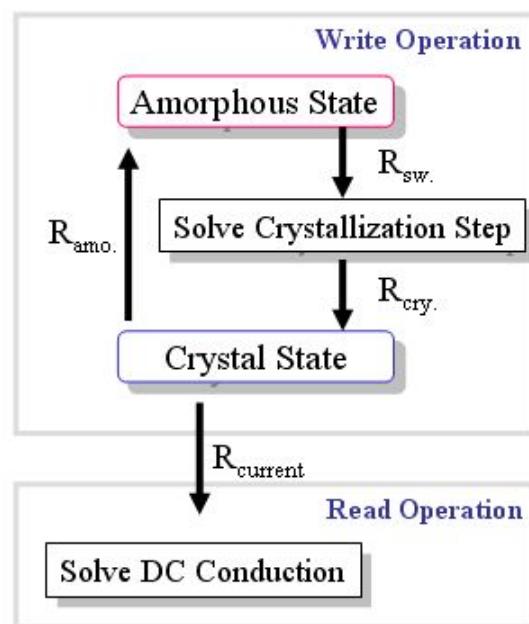

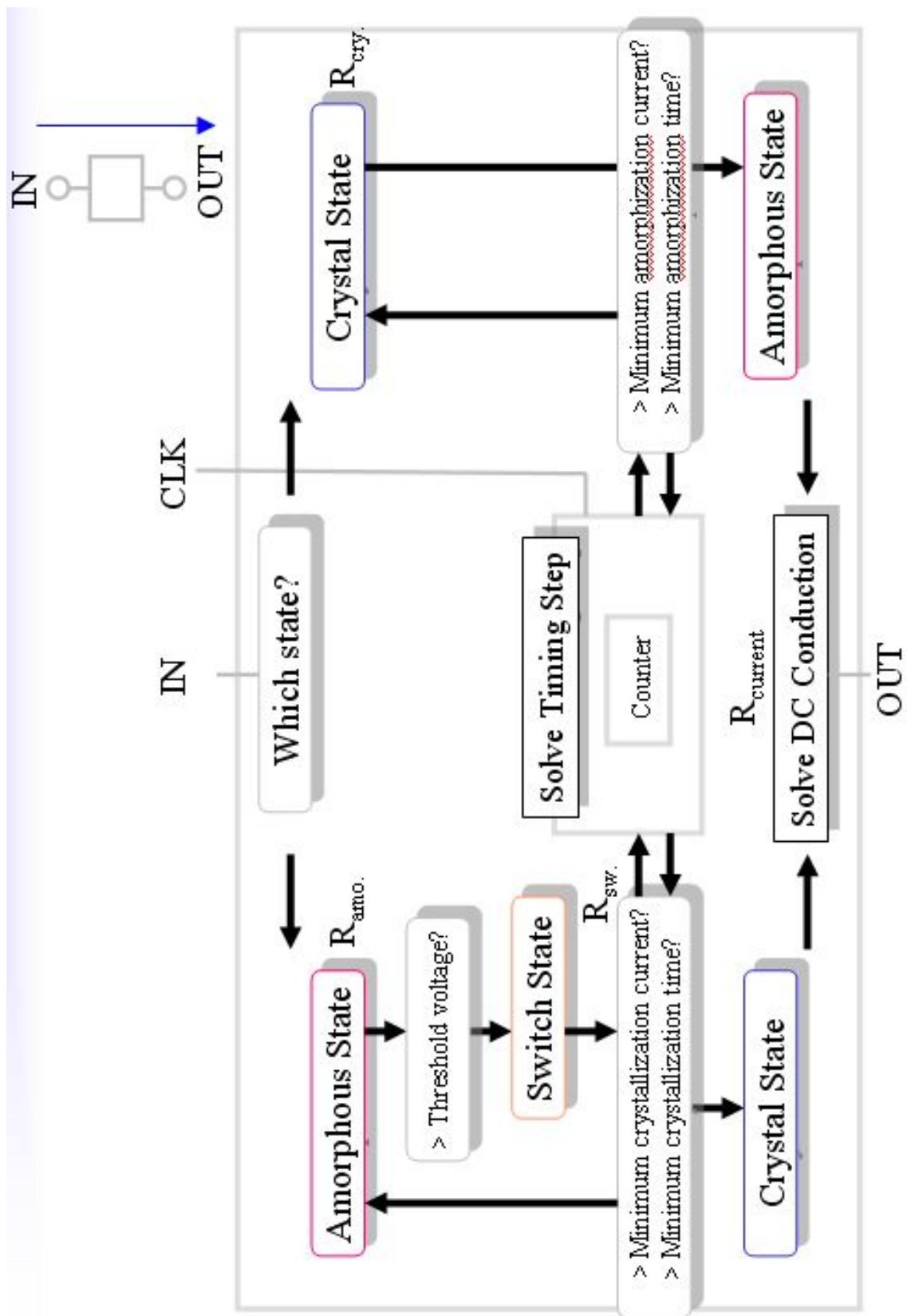

従来にも、同様の観点から、SPICEプリミティブモデルを組み合わせて相変化素子シミュレーションモデルを作成する研究[39][40]が報告されている。しかしながら、従来の研究ではSPICEモデルの組合せで構成される以上、動作を記述するには無駄が多く、余分なリソースを消費してしまう。これは、大規模なメモリ回路を検証する上で現実的ではない。そこで、本稿ではこの素子特性をアナログ記述言語Verilog-Aを用いて、必要最低限の動作を書き出し、よりフレキシブルなシミュレーションモデルを作成した。図2-10に処理の大まかな流れを、図2-11に詳しい流れを示す。厳密に熱伝導式を解き求めることが可能であるが、ここでは、従来のspiceモデルと同様に状態の遷移のみを行うとする。このモデル構造は、内部に結晶状態、非晶質状態、スイッチ状態の3状態を持つ。電流が入力されると、自身が結晶状態か非晶質状態かによって異なった処理を行う。それぞれの遷移条件により、素子抵抗値が一意に選択され、電流が算出される。

図 2-11 簡易熱計算モデル詳細構造

図 2-12 簡易熱計算モデル構築ポイント

この簡易熱計算モデルを構築するにあたって、演算量削減の観点から、3種類の線型モデルを用いて構築している。図 2-12に示す3本の黒線画モデル、青色赤色がそれぞれ、結晶状態、アモルファス状態の実測値から得られた波形である。特に気にかけたポイントは次の5つである。

1. READ 動作電圧時のフィッティング：

この付近の電圧は論理値を読み取る上で重要である。もし、詳細なモデルにしたいならば、連続書き込みの抵抗減少追従や、この後の多値にも対応できる。

2. 閾値：

実験値より、値さえ判明すれば、Verilog-A 構文で簡易な電圧比較構文を表現できる。

3. SW後抵抗：

スイッチング現象を引き起こした後は非線形に抵抗値が下がっていく。これに追随するために3本目の波形を作成した。

4. 再非晶質化：

スイッチング現象を引き起こし、低抵抗な状態のセルに、電流が過度に印加され、電流がリセット領域に至ってしまうと、再非晶質という

5. 結晶化時間

この時間制約に関しては、実験結果より得た値を基に、電流印加時間を clk 周期をカウントし、条件判別している。同様の手法を適用し、連続読み取りアクセスによる状態遷移等も表現することが出来た。

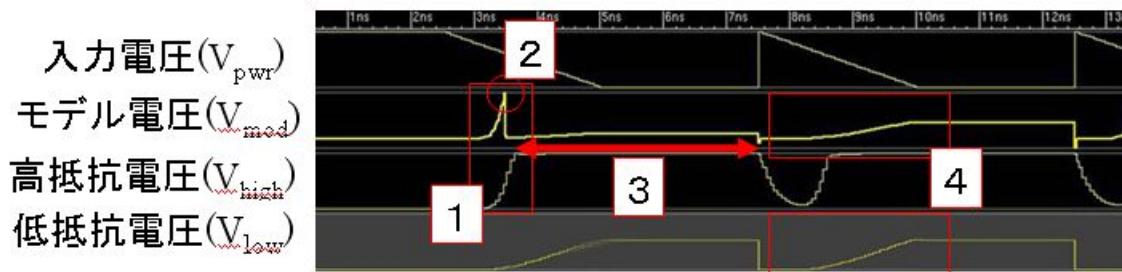

図 2-13 簡易熱計算モデルテスト回路

図 2-14 簡易熱計算モデルシミュレーション結果

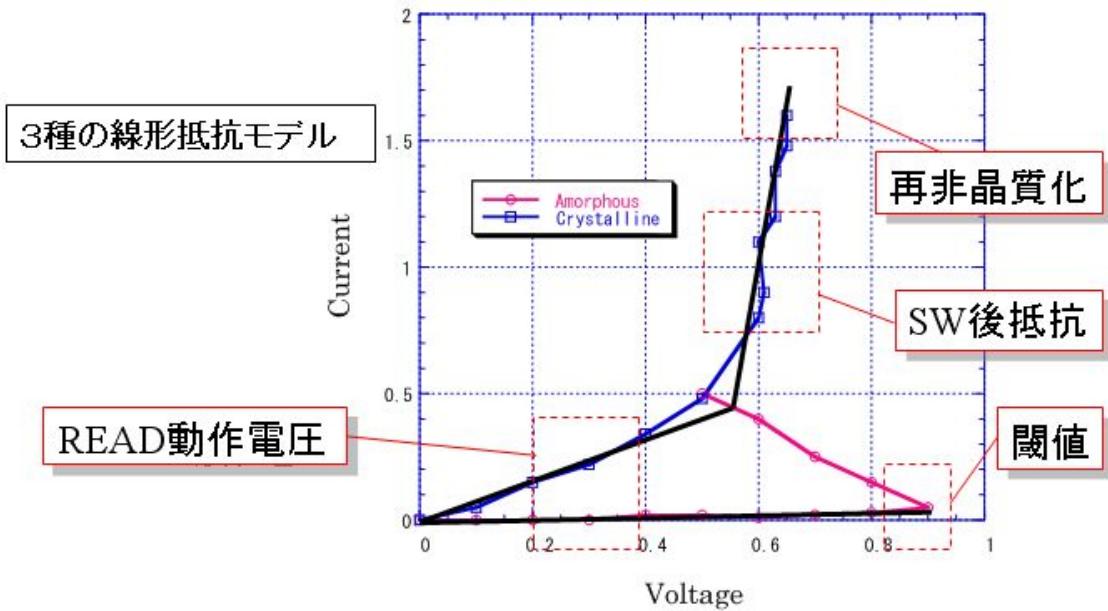

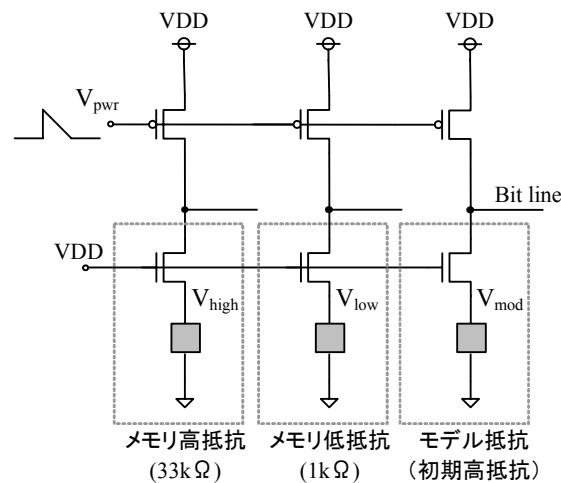

図 2-13にこの簡易熱計算モデルを動作テストしたテスト回路を示す。この回路にはカルコゲナイト半導体の高抵抗と低抵抗を仮定した抵抗と、モデル抵抗（初期状態は高抵抗）が接続されている。この時、それぞれに繋がっているPMOSをオンにしていくと

1. 高抵抗電圧フィッティング：

初期状態が高抵抗なので、高抵抗と同じ電位の上がり方をしている。

2. スイッチング現象再現：

しかしながら、閾値電圧に達した瞬間、モデル抵抗だけ低抵抗にスイッチングしたことが見て取れる。

3. 結晶化時間：

このまま、結晶化時間を越える間、電流を印加し続ける。

4. 低抵抗電圧フィッティング：

再び、PMOSをオンにすると低抵抗と同様の電位の上がり方を示す。これは高抵抗から低抵抗への遷移が成功したことを示す。

## 第3章 相変化不揮発性メモリ

### 3-1 記憶原理

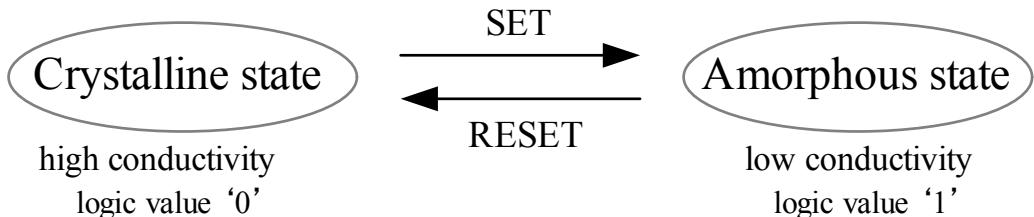

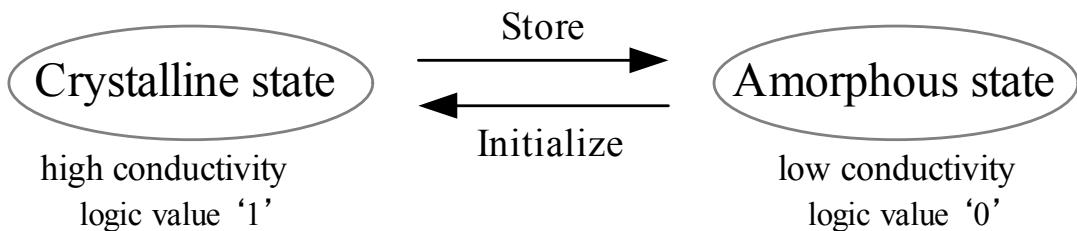

図 3-1 2値記憶での状態遷移

図 3-2 2値記憶メモリの二つの状態

電気的に書き換え可能な不揮発性メモリを実現するためには、異なる 2 つの安定な状態が必要である。本不揮発性メモリの場合は、図 3-1に示すように、結晶状態と非晶質状態がこの 2 つの状態に相当し、この状態の抵抗値の違いを論理値の “0” と “1” に対応させている。これらを模式的に表すと図 3-2になる。図 3-2のAが非晶質状態に、Bが結晶状態に相当する。非晶質状態は厳密には準安定状態であり、図 3-2に示すように自由エネルギーの極小値をとる。図 3-2に示す  $dE$  が大きくなると安定性が良くなるが、書き換え時に大きなエネルギーを必要とする為、転移が困難となる。逆に、 $dE$  が小さいと容易に書き換えできるが、安定性が悪くなることを示している。このような相転移現象は種々の物質で観測されるが、その中でも、6 族元素を主成分としたカルコゲナイト半導体は適度

な安定性と書き換え特性を示す。

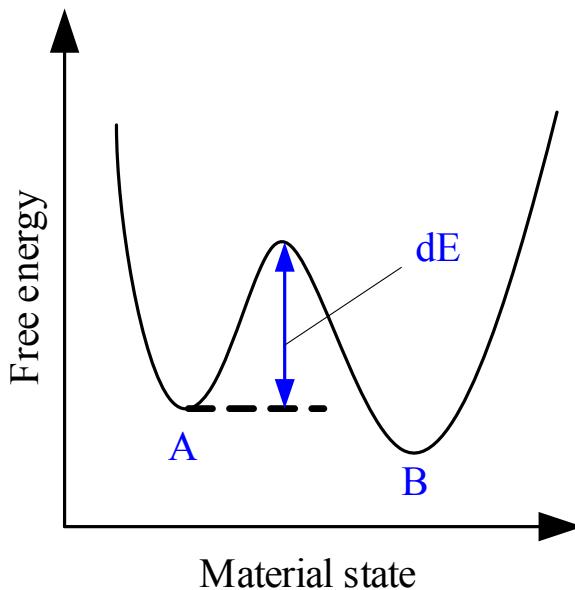

図 3-3 カルコゲナイト半導体の IV 特性

図 3-4 書き込み消去パルス

図 3-4に書き込み消去パルスとそれに伴う資料の温度変化の概略を示す。最初に結晶（低抵抗）化過程について述べる。高抵抗な非晶質状態の試料に電圧( $V_{set}$ )を加えていくと、閾値電圧( $V_{th}$ )でスイッチング現象を示し、試料は低抵抗な状態になる。この状態では試料に大きな電流が流れ、その電流による発熱で試料温度が上昇する（自己加熱）。試料温度が結晶

化温度( $T_c$  以上かつ融点( $T_m$ ) 以下で, ある一定時間( $t_{in}$ ) 以上保持されれば( $t_{cry} > t_{in}$ ), 試料は低抵抗な結晶状態へ遷移する. この結晶(低抵抗)化過程をセット動作と呼び, この時加えるパルスをセットパルスと呼ぶ. 結晶化にはある一定時間[29]が必要である. そのためスイッチング現象直後にパルス印加をやめると試料は結晶化しない. よってこの過程では比較的長い時間の電流パルスが必要で, メモリの動作速度は結晶時間に左右される. 逆に, 高抵抗な非晶質状態にもどすには, 試料を  $T_m$  以上に加熱し急冷させる. 冷却に時間がかかる(冷却速度が遅い)と試料は結晶化してしまう. そのためこの過程では, 比較的幅が狭く大きな電流パルスを加えている. なおこの時, カルコゲナイト半導体をはさむ上下電極は, 放熱(冷却)板としても重要な役割を果たしている. この非晶質(高抵抗)化過程はリセット動作と呼ばれ, 使用する電流パルスはリセットパルスと呼ばれている.

以上のような 2 種類のパルスを用いて書き込み消去を行っている. この各状態は構造変化を伴った変化であり, 電源を切っても状態は, 保持されるので不揮発性メモリとして利用される. なお抵抗値の読み出しには, 試料が転移(相変化)しない低い電圧パルスを加えて行う必要がある.

### 3-2 メモリセル構造

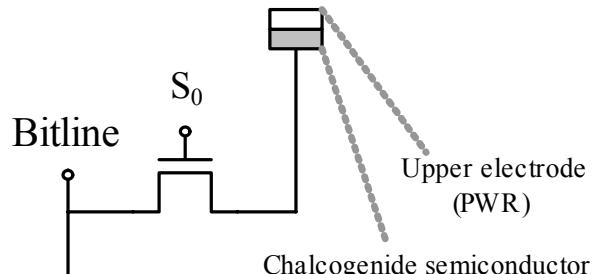

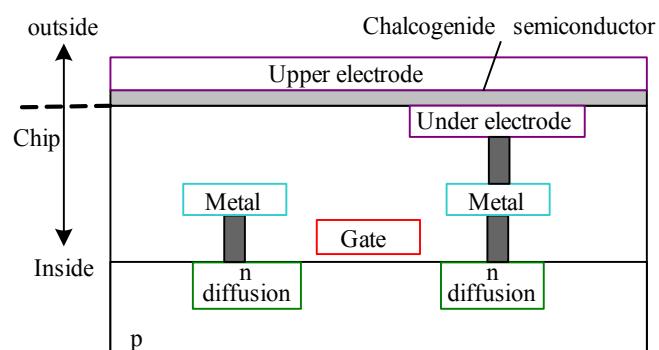

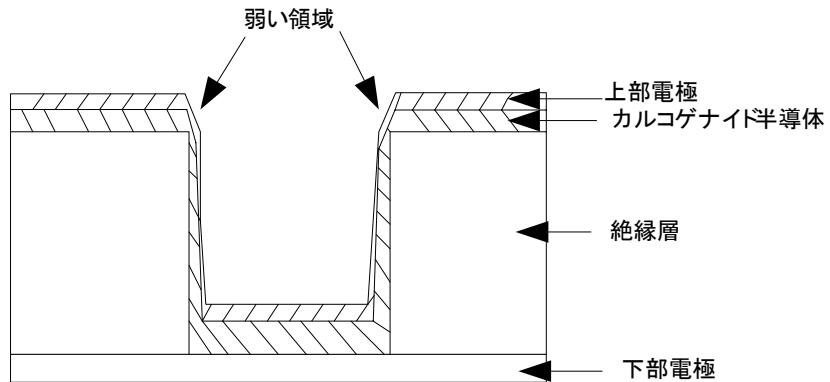

図 3-5 メモリセル構造

図 3-6 メモリセル断面図

図 3-5にメモリセル構造を図 3-6にその断面図を示す. メモリセルは図 3-5に示

すようにNMOS1個と記憶材料であるカルコゲナイト半導体の1T1Rで構成される。この様な単純な構成の為、小面積から高集積化／大容量を見込める特性を持っている。NMOSとカルコゲナイト半導体との接続は、図3-6に示すようにメモリセルから垂直に配線層を接続していき、上部絶縁層まで至る設計を行う。その後、製造されたチップには絶縁層が作成されるが、この絶縁層にコンタクトホールを加工作成し、配線層をむき出しにして、下部電極とする。この加工後、カルコゲナイト半導体薄膜と上部電極をそれぞれスパッタ法によって作成する。以上の説明の通り、カルコゲナイト半導体は上下電極で挟まれる単純なサンドイッチ構成を取っている。この単純な構成から、特殊な装置を使用せずとも製造が比較的容易に行える。2章で述べたように、このカルコゲナイト半導体に電気的なプロセス、つまり、電流を印加することによって発熱させ、状態変化を引き起こしている。この熱的な影響については、必要に応じて後述するが、状態変化しているカルコゲナイト半導体、直下に存在するCMOSへの影響は分厚い配線層によって生じることはない。

### 3-3 メモリセルとしての性能

メモリ素子に要求される性能は、書き込み消去回数、書き換え速度、データ寿命、消費電力に集約される。これらについて次に詳しく述べていく。

#### 3-3-1 書き込み消去回数

書き込み消去回数を増やすには[41]

- ・ 偏析や相分離が起きない

- ・ 体積変化が小さい

- ・ 形成される結晶相の種類が少ない(一つが望ましい)

- ・ 結晶相が複数ある場合、融点の差が小さい

等の性質が要求される。

单一元素のみで、相変化型不揮発性メモリが実現できれば好ましい。しかし、单一元素のみで、適当な結晶化温度や融点等を示すものが存在しないため、多元系の材料を使用しなくてはならない。多成分系の組成を使った場合、書き込み消去を続けると偏析などを起こすことが考えられる。同一ビットに繰り返し書き込み消去を行うと、そのビットの記録部は融解と凝固を繰り返す。融解は中央部から、凝固は周辺部分から始まる。化学量論的組成(例えば、GeTe等)以外では、凝固時(融点以上から、融点以下になる段階で)に、記録部を構成する元素又は化合物が先に凝固する成分と後で凝固する成分とに分離することがある。後で凝固する成分は周辺部分からの凝固の進行に伴い中央部へ移動して、濃度

が周辺部で低下、中央部で上昇、そして偏析し、書き込み消去回数の減少に繋がる。

また、融点の低い母相に高融点の小さな結晶相が析出すると、リセットパルスを加えることで、母相が容易に溶けても高融点の結晶相が溶け残ることが考えられる。書き込み消去を繰り返すことにより、この結晶相が成長し、アモルファス結晶間の相転移が困難になり、書き込み消去に支障を来たす可能性も考えられる。

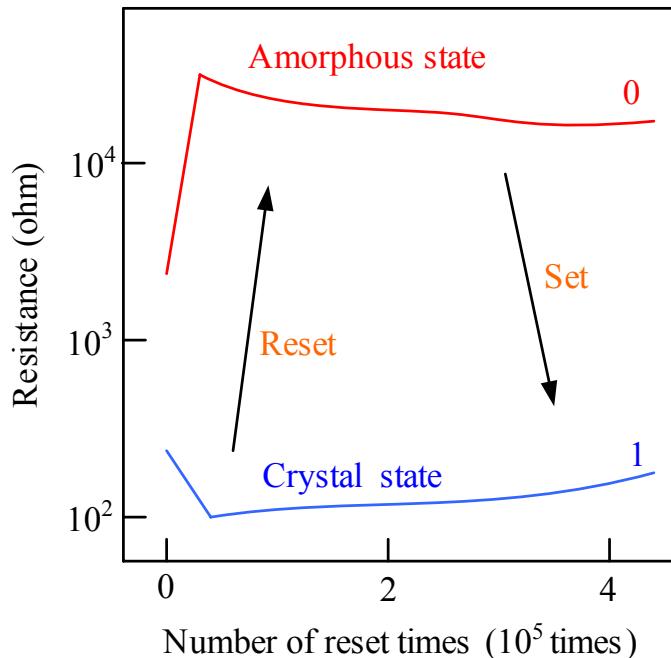

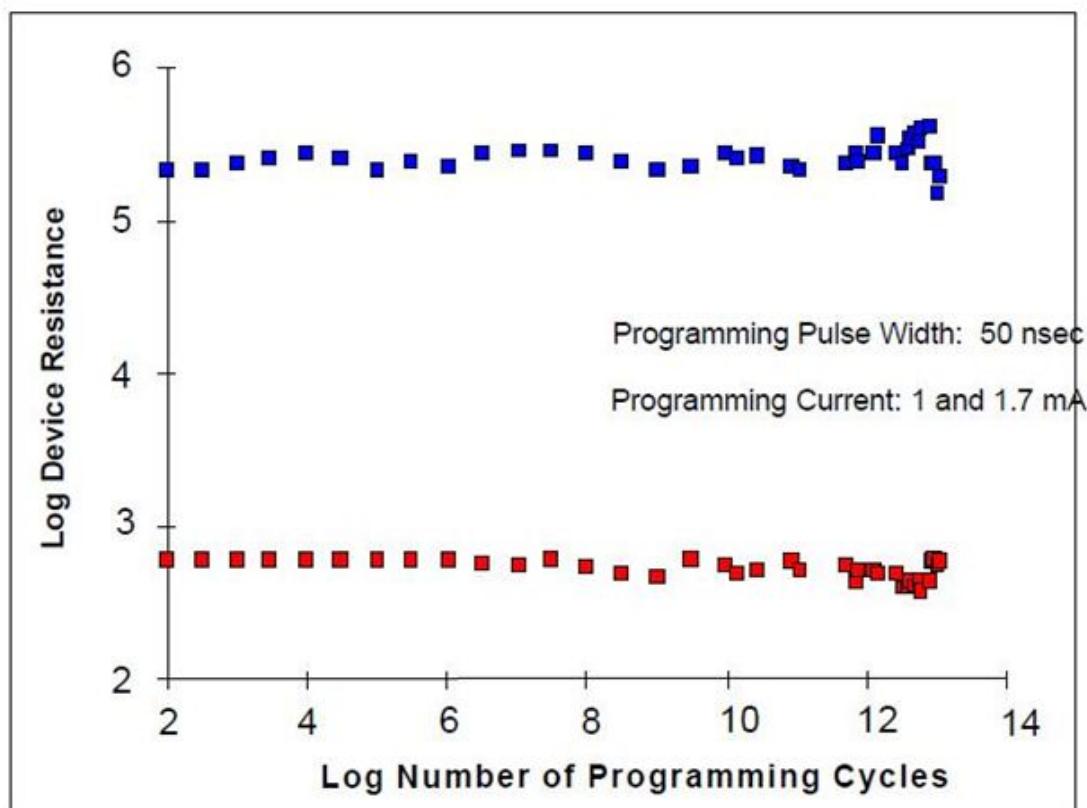

図 3-7と図 3-8に当研究室で実験を行ったAbSbTe系の書き込み消去回数と、Ovonyx社にて行われたGeSbTe系の書き込み消去回数を示す。Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>系の素子では、10<sup>12</sup>回以上の書き込み消去が発表されている。一方AsSbTe系の材料では、そこまでには及ばないが 10<sup>5</sup>回以上の書き込み消去回数が測定されている。一般的に製品として耐えうるには 10<sup>10</sup>回以上の書き込み消去回数が問われるが、AbSbTe系は消費電力の点でGeSbTeに勝っている。

図 3-7 書き込み（リセット）パルスの回数と抵抗値変化（AsSbTe）

図 3-8 書き込みパルスの回数と抵抗値変化（GeSbTe）

### 3-3-2 書き換え速度

表 3-1 相変化材料の結晶構造と結晶化時間

| 組成                                                         | 結晶構造                                                | 結晶化時間             |

|------------------------------------------------------------|-----------------------------------------------------|-------------------|

| $\text{Te}_{6.1}\text{Ge}_{1.5}\text{Sb}_2\text{S}_2$      | 複合相: $\text{Te}+\text{GeTe}+\alpha$                 | 数 $\mu\text{ s}$  |

| $\text{Te}_{9.3}\text{Ge}_5\text{As}_2$                    | 複合相: $\text{Te}+\text{GeTe}+\text{As}_2\text{Te}_3$ | 数 $\mu\text{ s}$  |

| $\text{Te}_{8.0}\text{Ge}_5\text{Sn}_{1.5}$                | 複合相: $\text{Te}+(\text{GeSn})\text{Te}$             | 数十 $\mu\text{ s}$ |

| $\text{Te}_{6.0}\text{Ge}_4\text{Sb}_{1.1}\text{Au}_{2.5}$ | 単一相: 単純立方晶                                          | 300ns             |

| GeTe                                                       | 単一相: 菱面体晶                                           | 100ns             |

| $\text{GeTe}-\text{Sb}_2\text{Te}_3$                       | 単一相: 面心立方晶                                          | 30ns              |

| $\text{Ag}_5\text{In}_5-\text{Sb}_{7.0}\text{Te}_{2.0}$    | 単一相: 六方晶                                            | 30ns              |

| $\text{Ge}(\text{Sb}_{7.0}\text{Te}_{3.0})-\text{Sb}$      | 単一相: 六方晶                                            | 30ns              |

本メモリは電気的に読み込みが可能であるため、読み出し時間は DRAM 等と同程度になる(表 3-1). また、リセットパルスを用いた非晶質化(リセット動作) もその性質上高速に行える(急速に加熱し急速に冷却をする必要があるため). 最も時間のかかるプロセスは、セットパルスを用いた結晶化過程(セット動作) である. よって、高速なメモリ素子の実現には、結晶化速度の早い材料が必要となる. 結晶化速度が早い材料は、

- ・ 結晶相が単一相である

- ・ 原子の拡散速度が速い

- ・ 結晶状態と非晶質状態の原子配置が似ている

等の性質を有している[42][43]. 表に主な相変化材料の構造と結晶化時間を見ると、1970 年代当時の材料では、結晶化に数十 msec かかっていた[44][45]. これに対して現在使用されている相変化材料では、結晶化時間が数十 nsec から数 nsec オーダーにまで短縮されている. この進歩の最も大きな理由は、現在の相変化材料が単一相に結晶化することである[46][47].

### 3-3-3 データ寿命

本相変化不揮発性メモリのデータ寿命を考えた場合、寿命に至るまでには幾つかの要因がある. 一つは、相変化の終焉である. 本メモリは結晶状態と非晶質状態の抵抗率の違いを利用して結晶化する. 結晶状態は熱力学的に安定な状態であるが、その一方、非晶質状態は、熱力学的に見ると準安定状態(図 3-2 参照) であり、十分な時間が経てば結晶状態へと遷移してしまう. よって、この非晶質状態の熱的な安定性がデータの保存寿命を左右する.

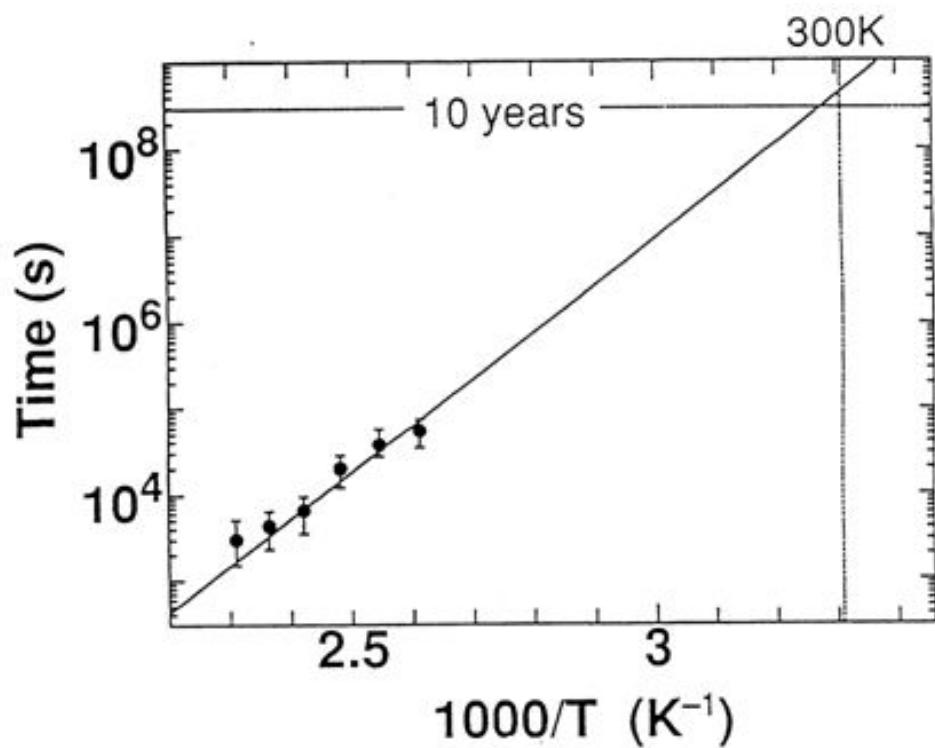

図 3-9 データの寿命 (GeSbTe)

図 3-9にGeSbTe系のデータ寿命を表した図を示す. 横軸が書き換え温度, 縦軸が書き換え回数である. このように, 書き換え回数が蓄積していくと, データの書き換える 温度が低下していくことが見て取れる. 結論として, 約 10 年で室温である300Kに至ると報告されている.

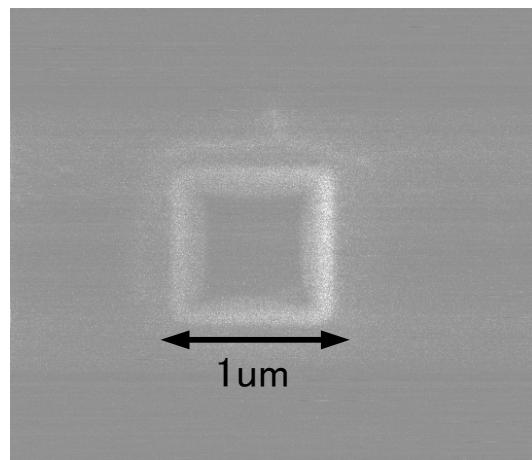

図 3-10 FIB による絶縁層

図 3-11 ストレスによる断線

もう一つの要因がメモリセル構造に起因する電気的なストレスである。次の節で詳しく述べるが、相変化型メモリは素子サイズを小さくすることによって、ある程度書き換え電流を減少できる。これは、相転移現象が熱的に起こるためメモリ材料の体積の縮小に比例して必要な熱量も減少するからである。図 3-10にFIBによる絶縁層の加工例、図 3-11に電気的ストレスを表す図を示す。このように、FIBによって絶縁層にホールを作成し、その上部にカルコゲナイト半導体層及び、上部電極層を作成する。この時、問題点として試料の活性な領域の端の部分は機械的にも電気的にも弱く、書き込み消去に伴う、電気的及び機械的なストレスによる影響を受けやすい。さらに、カルコゲナイト半導体は、書き込み消去時に4%の体積変化を伴う。この特性が更にストレスを生じ、セルを微細化していくほど、この影響は大きい。実際、記憶素子材料の特性実験過程においても、書き込み消去に伴う試料の劣化により急に抵抗値が大きな値に固定され、その後相転移が不能となる現象がしばしば観測された。これは書き込み消去にともない、電極部分に機械的、電気的なストレスが徐々に蓄積され、最後には断線したと考えられる。

改善策としては

- FIB で絶縁膜を加工するときに、階段状に加工することで、端を滑らかにする

- ホール加工後、絶縁膜全面に対し、膜圧低下のための加工を行う

- カルコゲナイト半導体層及び上部電極の膜圧を高くする

- 導電性のプラグを埋め込む

等が挙げられる。

もちろん、これは記憶素子の本質的な問題ではなく、プロセス上の問題である。メモリセル構造と、記憶材料及び上下電極間における物性の相性関わってくる為、十分に改良の余地はあるが、留意すべき事項である。

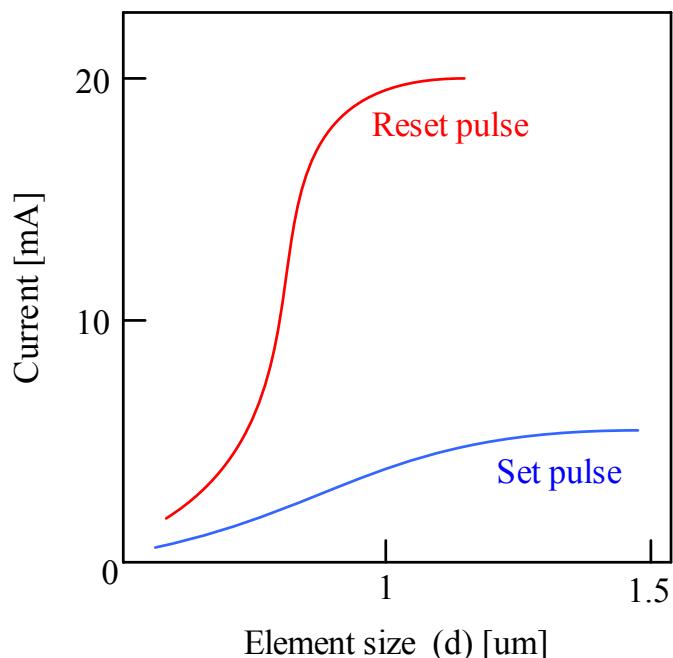

### 3-3-4 消費電力

第一章の背景で述べたとおり、低消費電力化は、メモリモジュールにとって非常に重要な問題である。特に、本不揮発性メモリでは、ジュール熱によって、書き換え消去にあたる相変化現象を引き起こしているが、このジュール熱の発生を、記憶素子への電流パルス印加によって行うため、電流値が大きくなる傾向がある。この問題は、動的消費電力の増大を引き起こすだけでなく、その大電流を素子へ印加できるようにするために、周辺回路のスケーリングを阻害する。つまり、メモリに対する重大な要求の一つである、高集積化を困難にさせる。

書き換え消去エネルギーを低減するには以下のことが考えられる。

- a) 記録素子の微細化

- b) 低融点記録材料の使用

- c) 素子構造の熱設計の点から見た最適化

- d) パルス形状の最適化

a)に関して

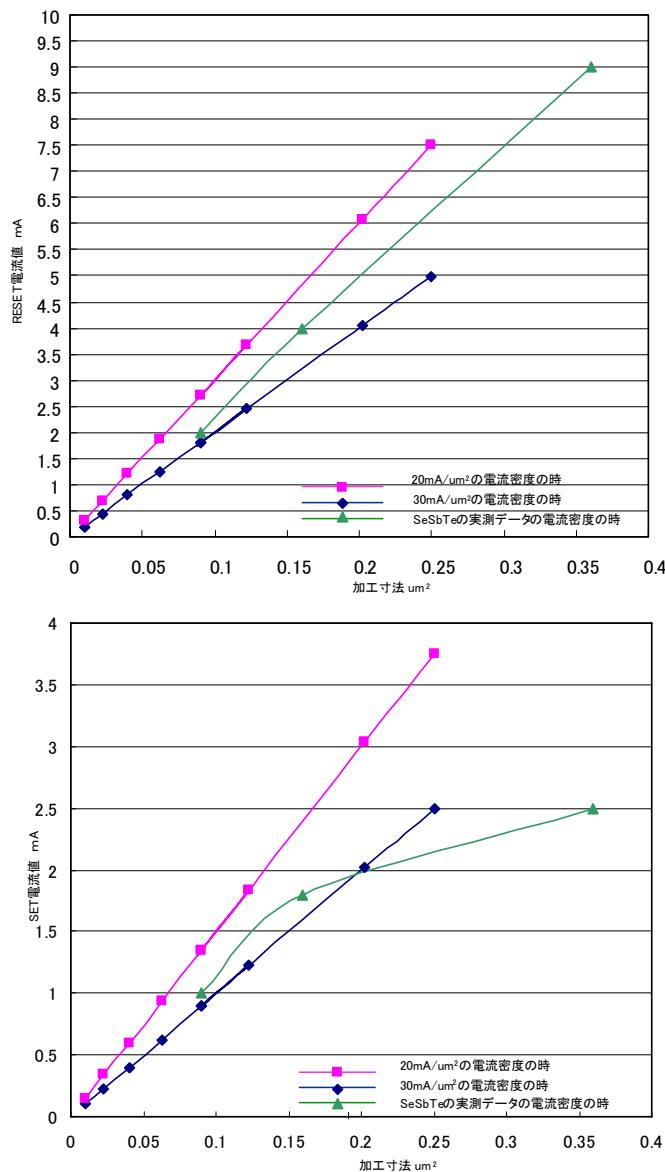

図 3-12 素子サイズと書き換え電流値の相関関係

微細化による書き換え消去電流の削減方法

ここでは相変化領域(記録部体積)を微細化し、低電流駆動する方法について述べる。なお、微細

化したときの特性を調べることは、実用化(特に大容量化の点で)にとって非常に重要であり、また記録部の大きさと書き換え電流値の関係は、前述のように回路設計にも非常に重要である。素子寸法と書き換え電流の関係を示している。素子サイズの直径が小さくなるにつれて、セット動作・リセット動作に必要な電流が小さくてもよいことがわかる。

| 組成                             | GeSbTe 系                                                             | AsSbTe 系                                                                | SeSbTe 系 |

|--------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------|

| 融点 [K]                         | 880～890<br>889<br>(Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> ) | 650～710<br>710<br>(As <sub>24</sub> Sb <sub>16</sub> Te <sub>60</sub> ) | 620～680  |

| リセット電流密度 [mA/μm <sup>2</sup> ] | 80～110                                                               | 20～30                                                                   | 20～30    |

| 結晶化時間                          | <100ns                                                               | <100ms                                                                  | <500ns   |

### 3-4 メモリ回路構成

#### 3-4-1 メモリセルアレイ

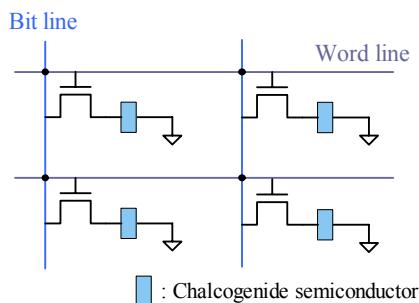

図 3-13 メモリセルアレイ

図 3-13にメモリセルアレイを示す。このようにメモリセルアレイはマトリクス構造を取っており、それぞれのメモリセルはアクセストランジスタと呼ばれるトランジスタ1個と、1つのカルコゲナイト半導体(1T1R)で構成されている。多値記憶メモリセルにして、メモリセル構造は2値記憶メモリセルと変わることはない。

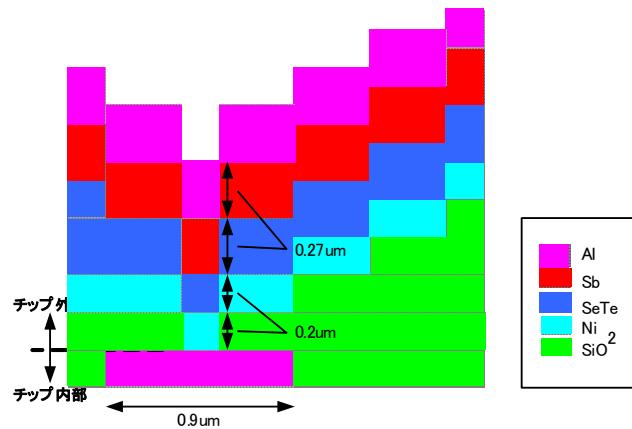

図 3-14 SeSbTe 膜の断面図

図 3-6にメモリセル断面図を示したが、そのメモリセル上部、チップ外部に記録膜であるSeSbTe膜が図 3-14に示すように蒸着される。記録薄膜は 3 章に述べた通り、既存 CMOSプロセスにて回路を設計する。この時、アクセストランジスタからコンタクトやVIAを通じ、最上位層メタルまで端子を伸ばしておく。チップ製造後に、チップ上部絶縁膜にFIBを用いて穴を空け、最上位配線層のAlまで至るコンタクトホールを形成する。その後、Niの層を形成し下部電極を形成する。その上に記憶材料であるSeTeの層及び、Sbの層を形成する。その上にAlの層を形成して上部電極としてメモリセルが完成する。また、これらの蒸着は既存CMOSプロセスに影響を与えることなく、低温プロセスで蒸着することが可能である。

### 3-4-2 メモリ回路構成

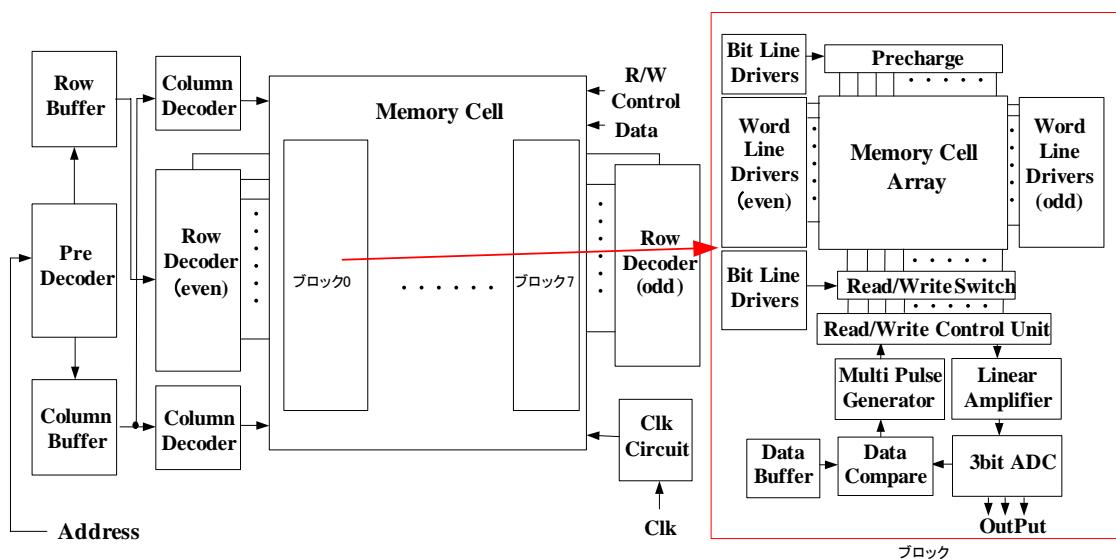

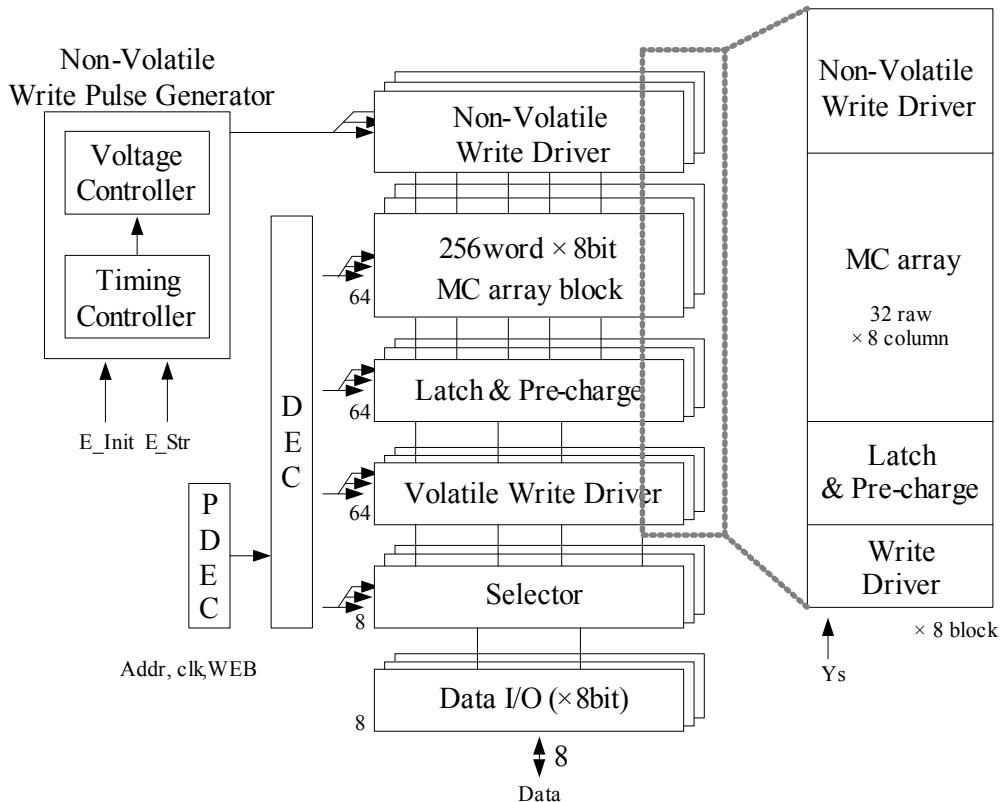

図 3-15 メモリ回路全体構成

多値(3bit/cell)メモリの全体構成ブロック図を図 3-15に示す.相変化メモリは, 不揮発性のため書き込み処理を行わない部分へは論理値を維持するための電源供給の必要はない.そこでメモリ素子へアクセスする場合は,メモリセルを1ワード毎に分割したメモリブロックを選択して対象となるメモリブロックのみを電源供給し, アクセスする構成になっている.これによって, 待機消費電力を削減している. なお, ワード線は抵抗が高いゲート配線を用いている為, メタル配線を並列に配線及び接続し, 並列抵抗として, 抵抗値の低減を行っている.

次に大まかにこのメモリコアの動作について説明する.

読み取り動作には, まず, 読みたいメモリブロックに電力供給し, 選択したメモリセルに読み出し電圧を印加することにより, メモリセルが接続したビット線にカルコゲナイト半導体素子の抵抗に応じた電圧が発生する.このビット線に発生した電圧を増幅させ, エンコーダ(もしくは, AD 変換器)に入力して出力される.

次に書き込み動作は, 素子へ電流パルスの印加回数によって行うためマルチパルスジェネレータを用いてセットとリセットに必要なパルス長とセルに書き込む値に対応したパルス回数を生成し, Read/Write スイッチ回路で電圧パルス信号を電流パルス信号に変換する. この変換されたセット, リセット電流パルス信号を選択されたメモリセルへ流し, 多値の書き込み消去を行う.

## 3-5 回路設計

### 3-5-1 設計仕様

回路設計に用いた素子パラメータについて, 表 3-2にまとめる.

表 3-2 設計に用いたデバイスパラメータ

| 項目          | 値など                                      | 補足                          |

|-------------|------------------------------------------|-----------------------------|

| 素子材料        | $Se_{15}Sb_{15}Te_{70}$                  | 多値化実験に成功した素子                |

| 接着面積        | $0.04\mu m^2 (0.2\mu m \times 0.2\mu m)$ | FIB で形成可能な電極面積              |

| 下部電極 / 上部電極 | Al+Ni / Al+Sb                            | 記憶素子を電極で挟むサンドイッチ型           |

| リセット電流密度    | $20\text{--}30mA/\mu m^2$                | SeSbTe 系の材料での値              |

| セット電流密度     | $9\text{--}14mA/\mu m^2$                 | 多値書き込みの電流密度                 |

| リセット電流値     | 1.2mA                                    | $30mA/\mu m^2$ の電流密度と接着面積から |

| セット電流値      | 560uA                                    | $15mA/\mu m^2$ の電流密度と接着面積から |

| リセット時間      | 100ns                                    | 測定されたリセット時間から               |

| セット時間       | 500ns                                    | 多値記憶でのセット時間から               |

|              |                   |                 |

|--------------|-------------------|-----------------|

| 抵抗値          | 40. 628k-836(8段階) | 多値記憶実験データから     |

| 高抵抗値 (結晶状態)  | 40.628k           | 測定された抵抗値        |

| 低抵抗値 (非晶質状態) | 800               | 測定された抵抗値        |

| スイッチング後の抵抗値  | 200               | 測定された抵抗値        |

| 素子閾値電圧       | 1.5V              | 測定されたスイッチング電圧から |

| 素子の書き換え回数    | $10^4$ 以上         | SeSbTe系の材料での値   |

また、メモリ回路の設計を行う上で必要になるのが、多くのトランジスタが連なるメモリセル部における寄生抵抗や寄生容量を考慮した設計である。特に相変化メモリは、素子による抵抗値を記憶の判断パラメータとして用いるため、寄生抵抗による影響がよりシビアである。そこで、SPICEシミュレーションで見積もれない部分については手計算を行い、寄生抵抗と寄生容量を以下のような式[48]により求めシミュレーションに加えた。512×1024bitのメモリコアを仮定し、見積もった値を表3-3についてまとめる。

表 3-3 寄生成分見積もり

| 項目                     | 値など      | 補足                                         |

|------------------------|----------|--------------------------------------------|

| もっとも遠いメモリセルへのビット線の配線抵抗 | 228.07 Ω | M1のシート抵抗 0.07 Ω/□<br>コンタクト 7               |

| もっとも遠いメモリセルへのビット線の配線容量 | 1.635pF  | EXTで抽出                                     |

| もっとも遠いメモリセルへのワード線の配線抵抗 | 366.43 Ω | M2のシート抵抗 0.07 Ω/□<br>コンタクト 7 Ω VIA1 1.03 Ω |

| もっとも遠いワード線の配線容量        | 663fF    | EXTで抽出                                     |

| ワード線へのメモリセル接続のゲート容量    | 4.43pF   | 1024Tr数で計算                                 |

| ビット線へのメモリセルの接合容量       | 10.78pF  | 1024Tr数で計算                                 |

### 3-5-2 メモリセル設計

我々が製造可能なメモリ構造と CMOS0.35um プロセスを用いて、アーキテクチャの実現性の確認をするため、相変化不揮発性メモリ回路の設計を行った。1024×512words のメモリセル数を仮定してメモリセルの設計、読み出し動作に必要な回路設計、書き込み動作に必要な回路設計を行う。

カルコゲナイト半導体に均一な電流が流れると仮定した場合SeSbTe系材料の電流値と素子領

域との関係を図 3-16 加工寸法と必要電流値で示す。

図 3-16 加工寸法と必要電流値

この  $\text{Se}_{15}\text{Sb}_{15}\text{Te}_{70}$  の書き換え消去の電流が最大に必要な場合を想定するとリセット電流密度が  $30\text{mA}/\mu\text{m}^2$  でセット電流密度が  $15\text{mA}/\mu\text{m}^2$  の時となる。図 3-16 でカルコゲナイト半導体の素子領域を  $0.04\mu\text{m}^2$  ( $0.2\mu\text{m} \times 0.2\mu\text{m}$ ) とした場合、必要なリセット電流値は  $1.2\text{mA}$ 、セット電流値は  $600\text{uA}$  となる。なお、この素子領域は集束イオンビーム装置 (FIB: Focused Ion Beam) を用いて、形成可能な最小の値とした。またリセット時間とセット時間、非晶質状態での閾値電圧は、測定された値から用いた。書き換え消去回数は、目安である。多値書き込み時の素子抵抗値は、測定データから得られた値を用いた。実際には、書き込みの際に素子抵抗値にばらつきが存在するが、多値記憶における素子

抵抗のばらつきの特性を評価したデータはない。よってシミュレーションの際の基準的な素子抵抗として実験データの値を用いた。

### 3-5-3 メモリセル周辺回路

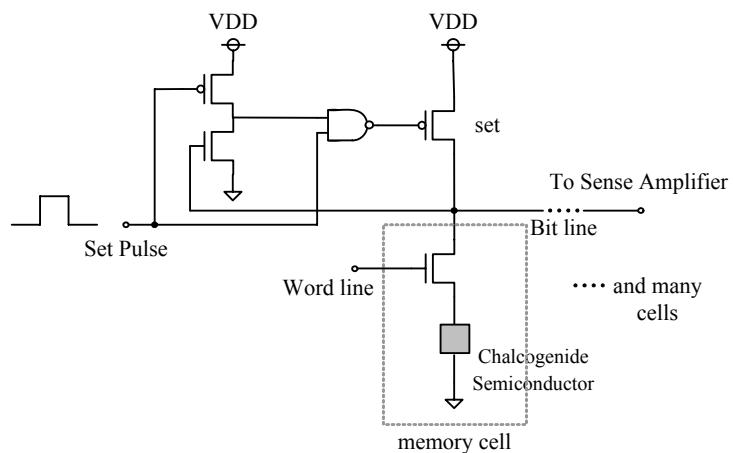

図 3-17 Read/Write 選択のスイッチ回路

図 3-17の下部に接続されているのが、1T1Rの本メモリセルである。これに対し、各ビット線には Read/Write選択のスイッチ回路がそれぞれ接続されている。このスイッチを構成する 3 種のトランジスタはそれぞれサイズが異なっており、書き込み時にはセット／リセットトランジスタを用い、読み出し時にはリードトランジスタを用いる。次に読み出し、書き込み動作と、設計最適化について述べていく。

### 3-5-4 読み出し回路設計

次に、読み出しを行う Read 用トランジスタのサイズ決定の条件は、書き込み消去の動作がおこらないように、トランジスタの駆動電圧をカルコゲナイト半導体のスイッチング電圧以下として設計ルールの最小である W サイズ 0.9um とした。

### 3-5-5 書き込み回路設計

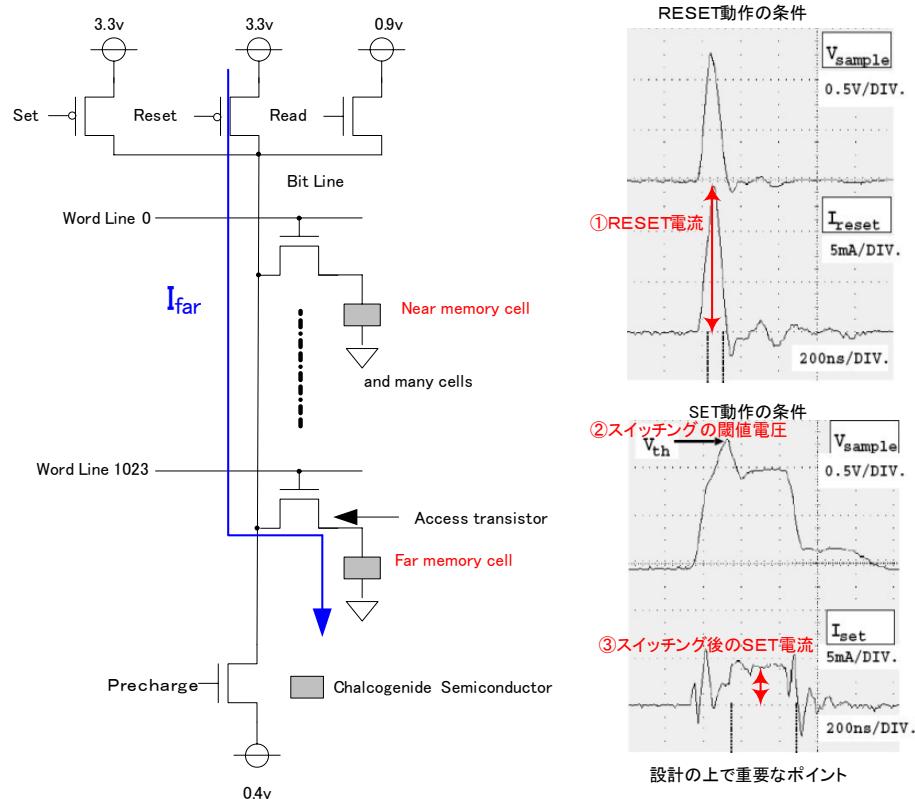

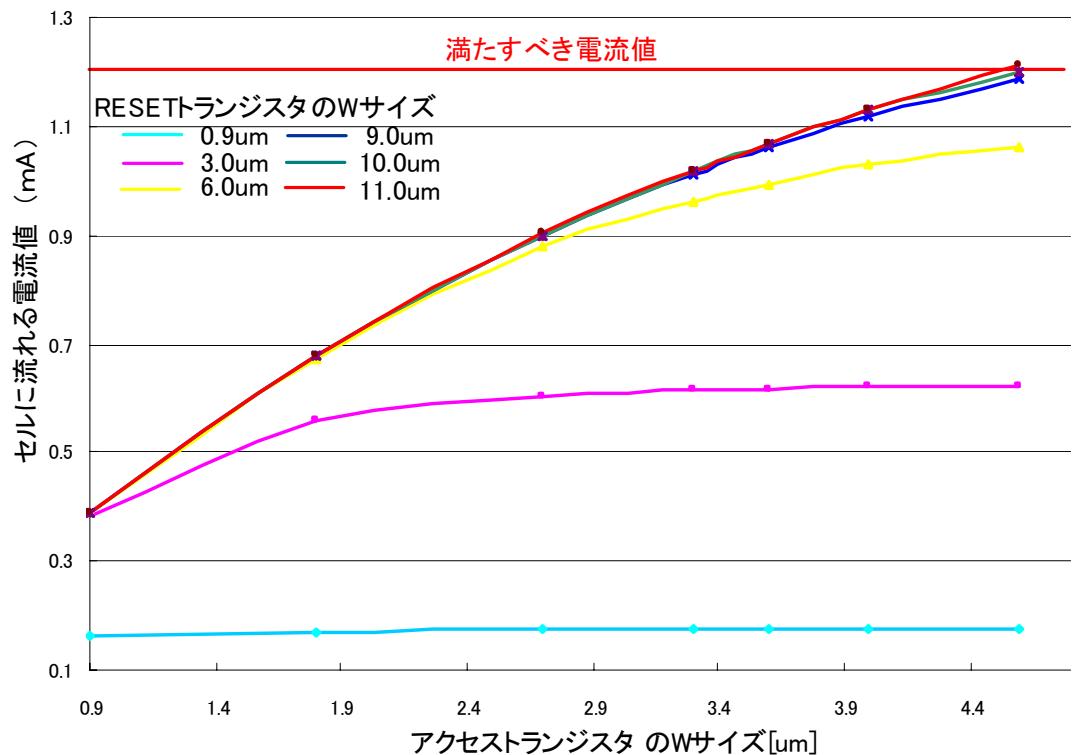

図 3-18 アクセストランジスタと RESET トランジスタの W サイズの決定のシミュレーション結果

図 3-19 SETトランジスタのWサイズの決定のシミュレーション結果

図 3-20 SET時の素子への印加電圧

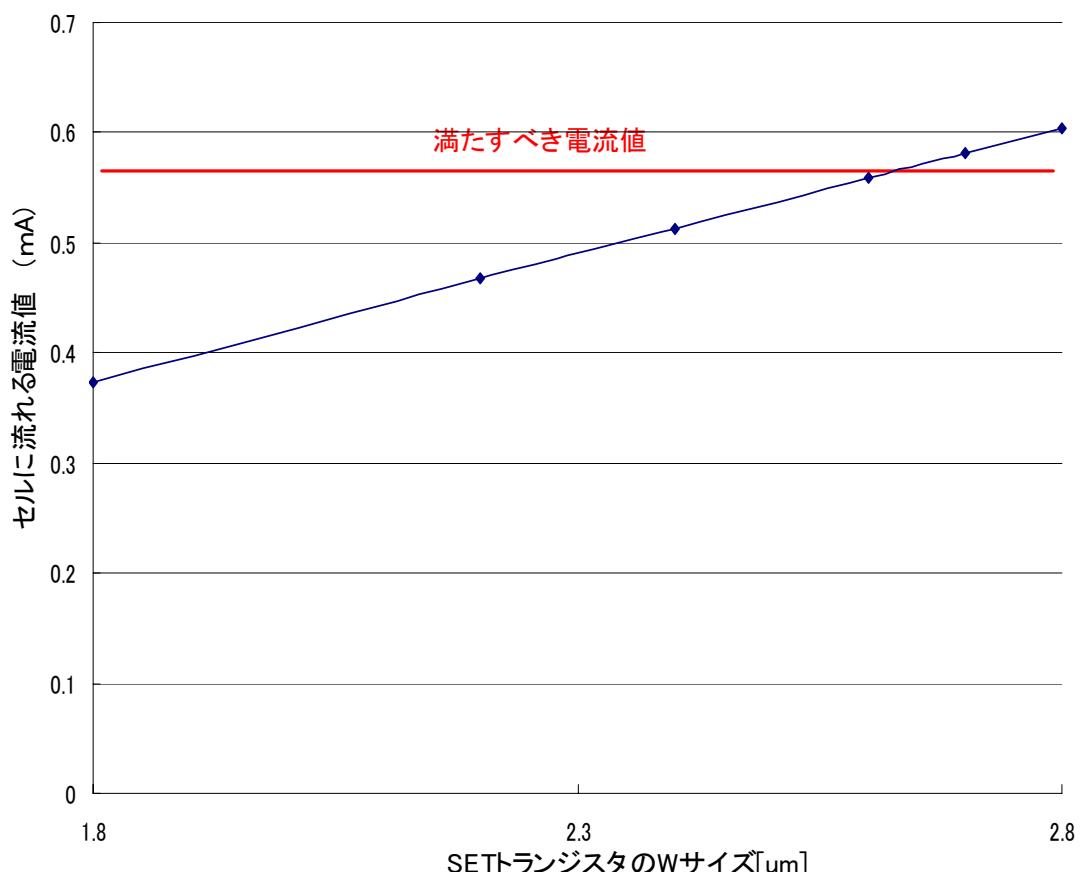

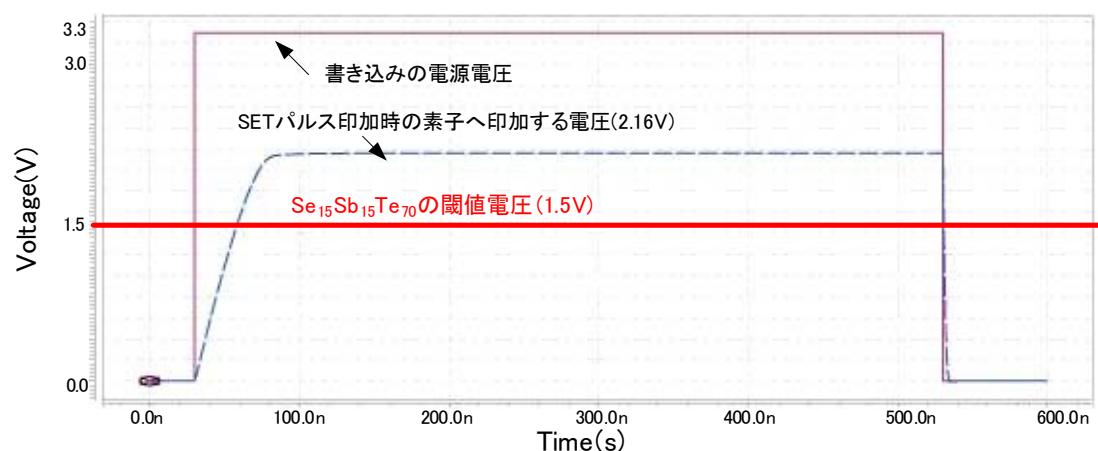

メモリセルのアクセストランジスタのサイズは、一番大きな電流値流すことが必要なRESET電流値によって決定される。BIT線には、メモリセルが連なるためビット線の寄生抵抗や容量が影響を考慮する必要がある。今回の設計では、ビット線には、1024個のセルを仮定している。1024個目のもつとも遠いセルへ 1.2mAが流すことのできるRESET用のPMOSトランジスタとメモリセルのNMOSのアクセストランジスタのサイズの組み合わせが必要になる。0.35umプロセスを用いているので、トランジスタのゲート長は最小である 0.4umと固定してゲート幅を可変にしたHSPICEシミュレーションを行った。また、素子抵抗値を低抵抗な状態の  $800\Omega$ とした。結果を図 3-18に示す。シミュレーションの結果、メモリセルのアクセストランジスタのゲート幅は 4.6umとし、RESET用のトランジスタのゲート幅は 11.0umとすることでRESET電流の仕様を満たすことを確認した。次にSET動作のためのSET用トランジスタのサイズ決定のためのシミュレーションを行った。SET動作は、第1にスイッチングの閾値以上の電圧を印加することが必要となる。第2にSET電流の仕様である 560uAを満たすことが必要になる。アクセストランジスタをW:4.6umと固定して、SETトランジスタのWサイズの決定を行った。シミュレーション結果を図 3-19に示す。シミュレーションの結果より、SET用トランジスタのWサイズを 2.7umとした。そして、図 3-20にSET動作時にカルコゲナイト半導体に印加する電圧値を示す。閾値電圧 1.5V以上の電圧を印加できていることが確認できる。

### 3-5-6 メモリセルレイアウト

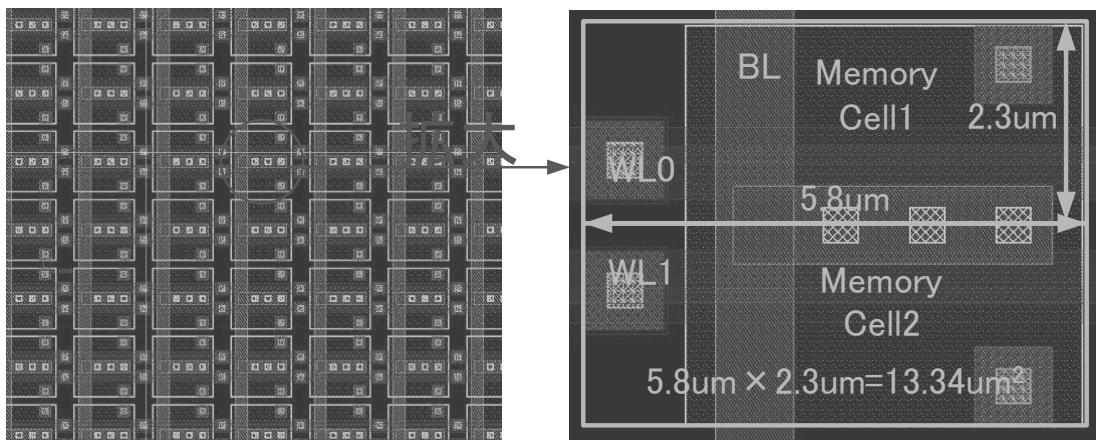

図 3-21 メモリセルのレイアウト

この結果をもとにして、メモリセルについてレイアウト設計を試みた。図 3-21に示す。1 メモリセルは、縦 2.3um 横 5.8um となり面積は、 $13.34\text{um}^2$  になった。よってメモリセルは、 $109\text{F}^2$  に相当する。しかし、3bit/cellの記憶密度を行えるため、ビット当たりのセル面積は  $36\text{F}^2$  となることを確認した。

### 3-5-7 設計に考慮すべき諸問題

本メモリ設計においては CMOS による回路設計技術以外に、カルコゲナイト半導体の特

性が密接に関連する。

設計時に考慮すべき事項の一つに熱問題がある。本メモリセルにおいて、現在保持している抵抗値を読み出す場合には、結晶化及び非晶質化が起こらない電流(読み出し電流)を印加してその値を読み取る。読み出し電流をデバイスパラメータより定められる セット電流の下限以下に設定すれば、一度の書き込みにおいて、状態遷移を起こすことは無い。しかし、実際は記録材料に熱を印加することによって相変化を引き起こし、書き込みを行っている為、同一メモリセルへの連続書き込みが行われると熱拡散が追いつかず、相変化素子の状態が変化してしまう。読み出し電流の大きさから、非晶質化に必要な $I_{str}$ を越えることは無いため、非晶質への遷移は起こることはない。しかし、その一方で、連続的な読み出し電流によって蓄熱した熱が結晶化に必要な熱量を持ち、その熱量を持続し、結晶化時間が満たされることで結晶化が進むこととなる。以上の事象と結果を纏めると、

- 現在が結晶状態の場合：

抵抗値が下がる。しかし、論理値には影響ない為、問題は無い。

- 現在が非晶質状態の場合：

非晶質状態から結晶状態へ遷移してしまう。論理的には0を保持しているはずのメモリセルが1を保持していると認識してしまう。

以上より、非晶質状態の場合、問題が生じる可能性がある。この熱問題対策に関しては、後述する各動作に対する安定化設計に関する記述の中で述べる。

また、もう一つ考慮されるべき熱問題として、隣接間セルもしくは同一メモリセル内で隣接する記憶素子の熱的影響がある。この問題に関しては、22nm 世代プロセスでも影響がないという報告[21]や、微細化として 22nm 世代まで目処が立ったなど報告[23]されている。

### 3-5-8 対策回路

#### 1. 热対策技術 (キャッシュ)

前述のような、同メモリセルに連続的に書き込みが行われたと仮定する。この時、あまりに書き込みが高速の場合は熱拡散が追いつかず、結晶化温度・時間を満たしてしまう可能性がある(セット動作条件が整う)。これは満たさないまでも、最大書き込み速度を制限する結果になる。そこで、書き込み時に前回のアドレスと値を、別途用意したレジスタへと保持する。そして、改めて書き込む場合、前回のアドレスと値をキャッシュした値と比較することで、熱的書き込み要因の速度制限を、約2倍延長することが可能となる。また

余分な回路による消費電力によって低消費電力とは異なる位置づけに感じられるかも知れないが、高い消費電力である書き込み消費電力を抑えることが出来るため、使用するアプリケーションによっては有用である。

## 2. 低消費電力化技術（ライトストップ）

リセット動作に比べ、セット動作は長時間（結晶化時間）の間電流を印加し続けなければならない。この時、消費する電力はリセット動作に比べ、2. 3倍大きい(CMOS0.35umプロセス)。このような状況の中で、既に書き込み先のセルが低抵抗の場合、無駄に大漁に電流が印加されてしまう。

図 3-22 ライトストップ回路

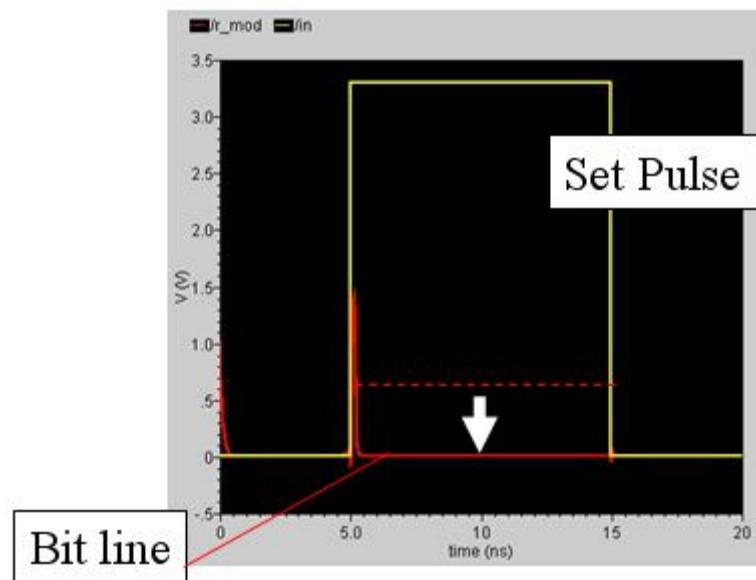

そこで、図 3-22のような回路を接続すると、書き込みセルが既に低抵抗の場合、ビット線の状態をフィードバックして、書き込みを止める機能を果たす（図 3-23）。赤線がビット線の電圧である。この回路によって、3 4 %の電力削減が見込まれる。

図 3-23 シミュレーション波形

### 3-6 結言

この章では、相変化不揮発性材料をCMOS回路上にて、どのような原理で動作させるか、その基本アーキテクチャの紹介及び動作を説明した。また、熱的要因な速度制限を改善するキャッシュ技術や、2値の書き込み時において一番消費電力の無駄が生じる、0保持セルに対する0書き込みを抑制するライトバックアーキテクチャを考案した。このアーキテクチャによって34%の消費電力削減が見込まれた。

## 第4章 多値化

### 4-1 目的

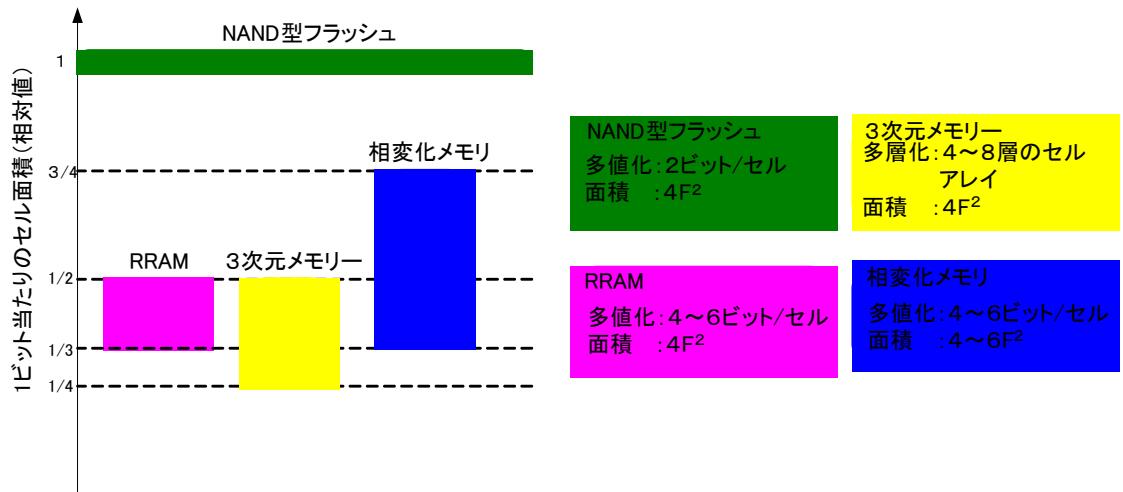

図 4-1 新型不揮発性メモリにおけるコスト競争力

第1章で述べたようにメモリにおいて大容量化は最も主要な方向性の一つである。本研究で扱う相変化不揮発性メモリ(PRAM)は、実質アクセストランジスタ面積のみという、1T1Rの単純で小規模なメモリセル構造を持っているが故に大容量化に向いている[49]。しかし、メモリセルのスケーリングによる書き込み電流低減化とは別に、ビット/コストを下げる方法が存在する。それが多値化である。PRAMは、その大きく変化する素子抵抗値という特徴を生かし、多値化によるビット/コストの削減への期待も大きい。

図 4-1に次世代、及び現在の不揮発性メモリにおける主流のNAND型フラッシュメモリに関する1ビット当たりのセル面積の比較を行っている。図から、多値化技術を用いることにより、ビット当たりの面積を下げる事が出来、ビットコストの低減に繋がっている。本相変化不揮発性メモリも、多値化技術を確立すれば、十分コスト競争に渡り合える可能性を持つ。第一章にも示したとおり、相変化不揮発性メモリの様々な多値化手法が提案されている。我々が提案する多値化手法は、他の方式に比べて書き込み時間を犠牲にする代わりに、書き込みにおける信頼性を確保して低電圧化に対応できるようにした方式である。この方式を用いて、メモリ回路のアーキテクチャを考案し、特許を取得した。また設計には、特許出願した本研究室で観測したデバイスパラメータを用い、回路シミュレーションを行った。動作時間や消費電力の見積もりを得て、メモリの面積効率の点を重視し、設計を行った。

## 4 – 2 多値特性実験

カルコゲナイト半導体の組成として GeSbTe が一般的に用いられているが、前節で述べた通り、本研究では SeSbTe を用いた[50]。その理由としては、GeSbTe の融点(880--890K)に対し、SeSbTe(650--710K)の方が低いからである。欠点として GeSbTe に比べ結晶化時間が長いことが挙げられるが、リセット電流を減少させることができ、消費電力を抑えることが出来るという長所がある。

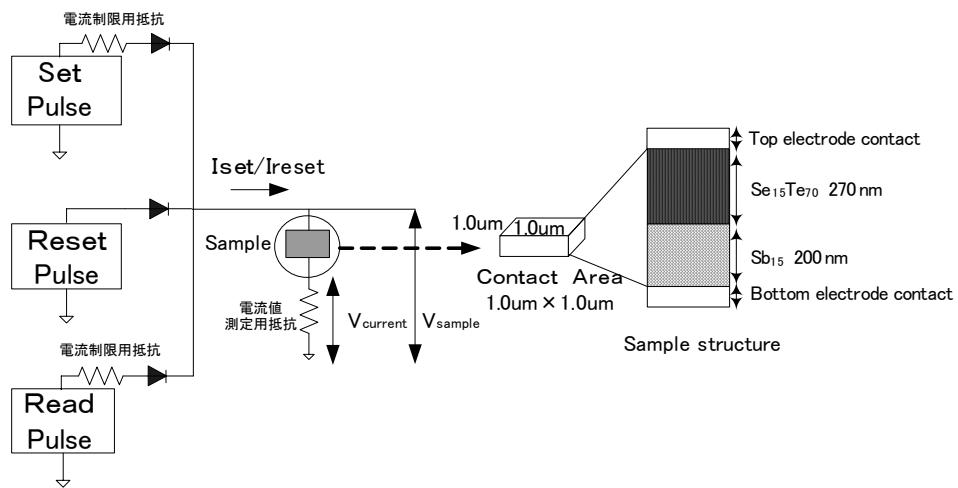

図 4-2 多値記憶測定回路

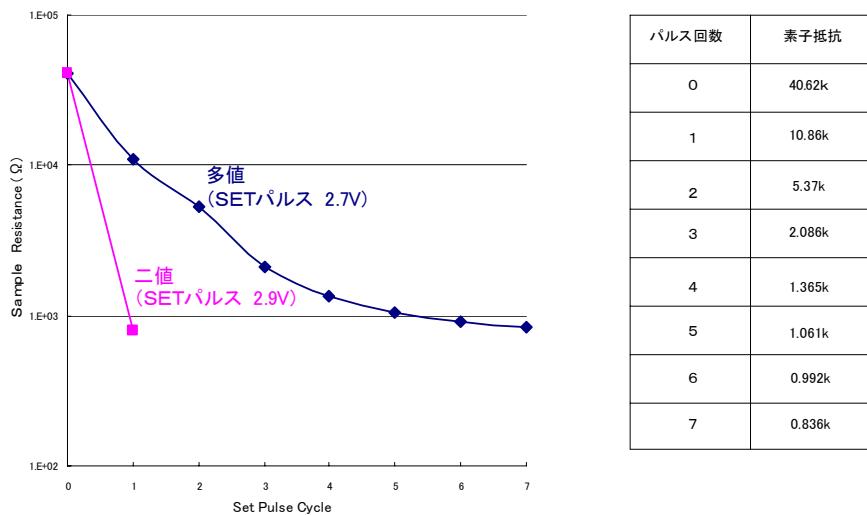

図 4-3 電流パルス印加によるカルコゲナイト半導体素子の抵抗変化

次に、多値書き込み消去の原理を述べる。我々は多値記憶特性を調べる為に以下の実験を行った。図 4-2に多値記憶測定を行った測定回路を示す。カルコゲナイト半導体素子を

電極で挟み、2値を書き込む為に用いている電圧値よりも低電圧(e.g. 2.7V)で 500nsec幅の電圧パルスを素子へと連続に印加した。その結果、パルス印加回数に従い、図 4-3に示すように素子抵抗が減少していくのが観測することが出来た。7回のパルス印加で、素子抵抗は  $40k\Omega$ ～ $836\Omega$  に変化することを観測した。

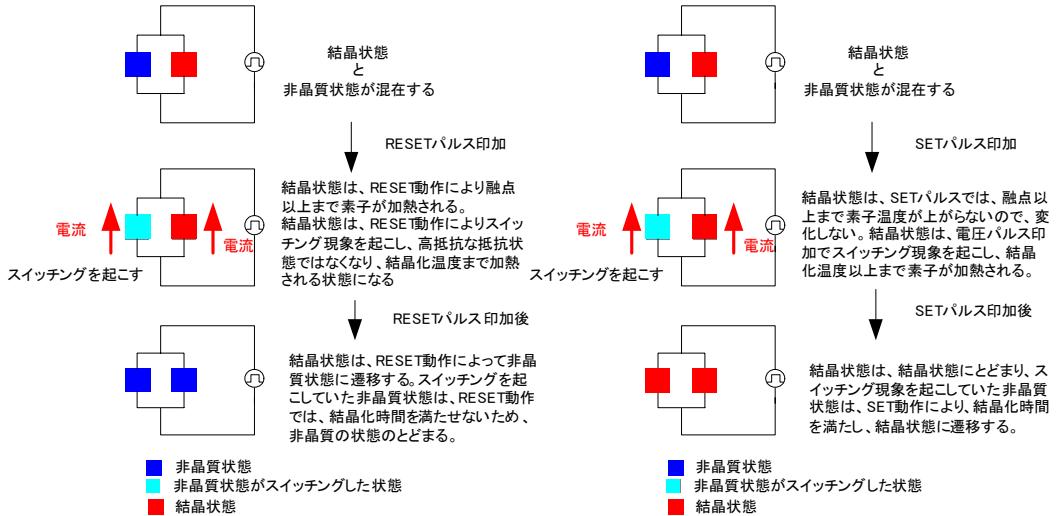

図 4-4 素子抵抗の多値化原理

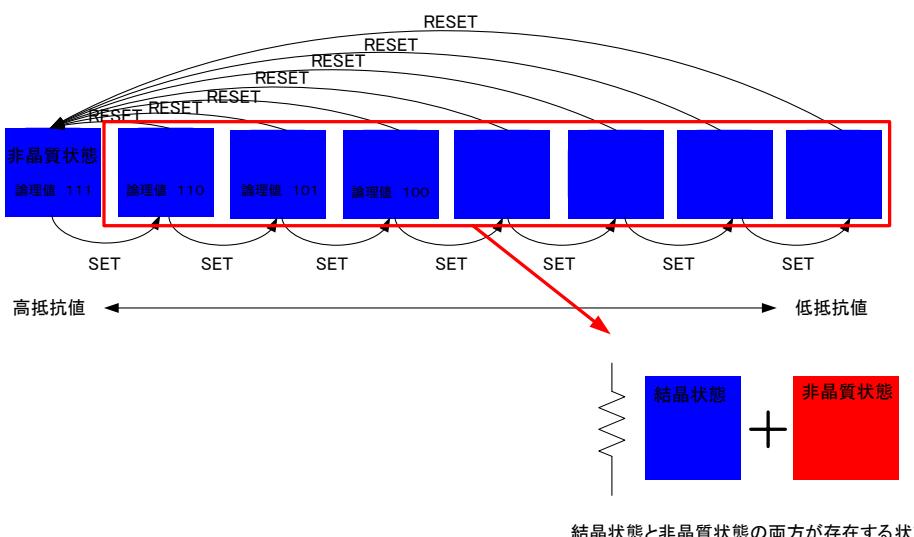

測定結果から 3bit/cell の多値化が可能になることが分かる。この現象は、電流パルスの印加を弱めて複数回に分割することで、記録素子であるカルコゲナイト半導体の状態が、非晶質状態から結晶状態への遷移が一度に全域で起こるのではなくて、部分的に状態の遷移が起きていると考えられる。つまり、図 4-4に示すように、素子の中に、結晶状態と非晶質状態と入り交じって中間値を定めていると予測される。

図 4-5 多値記憶の状態遷移図

多値記憶の状態遷移図を、図 4-5に示す。前述のように、多段階に変化した素子抵抗値へ論理値を割り当てることで多値論理を実現する。各状態はセット動作で遷移し、どの状態においても、リセット動作を行うことで高抵抗な非晶質状態へ遷移する特色を持つ。

### 4-3 読み出し回路設計

#### 4-3-1 読み出し方式

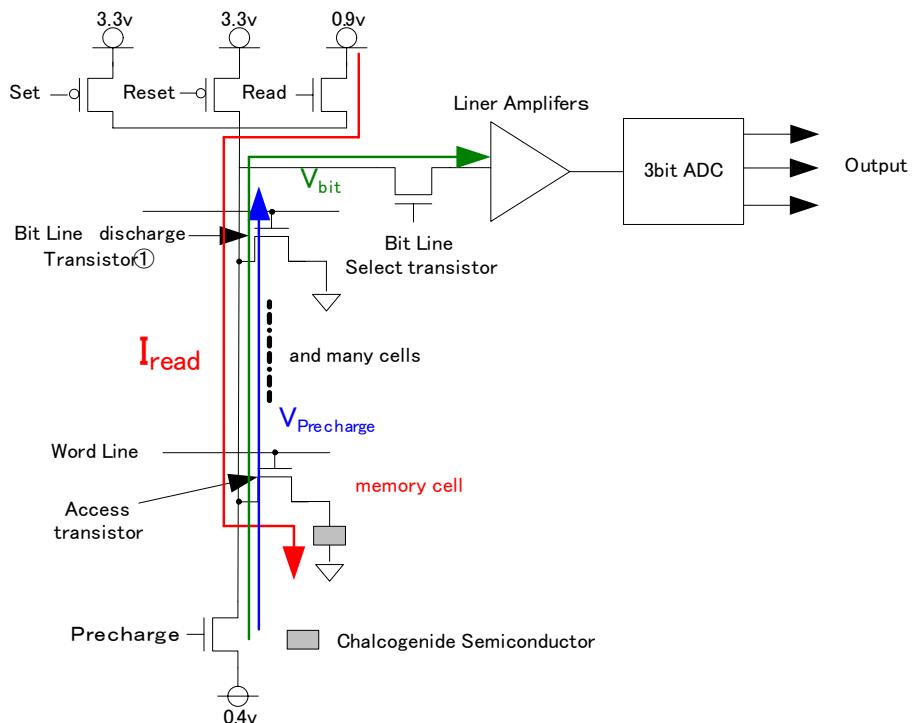

簡略化した読み出し回路構成を図 4-6に示す。各ビット線には、サイズの異なる 4 種のトランジスタ(Set/Reset/Read/Precharge)が接続されている。また、読み出し時に読み出しを行わないBIT線は①のトランジスタを用いて、GNDへ落とし消費電力削減を行う。読み出し動作は、まず読み出し時間を速くするために各ビット線をプリチャージ用のトランジスタをONさせて、ビット線を読み出し電圧の中間値あたりにプリチャージしてから読み出し動作を行う。次にアクセス/リードトランジスタを同時に動作させ、メモリセルに読み出し電流を流すと、ビット線にはカルコゲナイト半導体素子の抵抗に応じた電圧が発生する。しかし、書き込み消去が起こらないように読み出し電圧をカルコゲナイト半導体のスイッチングの閾値より低く設定してあるために、素子抵抗値に対応したビット線に生じる電圧の差が小さくこの電圧差判別して読み出しを行うのは、難しい。そこで、容易に電圧差を判別するために線形増幅器回路によってビット線の電圧を増幅させ、各素子抵抗で生じるビット線の電圧値の差を大きくしている。最後に増幅させた電圧値をAD変換器によって、電圧値を判別し、結果を出力して読み出し動作完了となる。

図 4-6 読み出し回路の構成

#### 4-3-2 回路構成及び動作

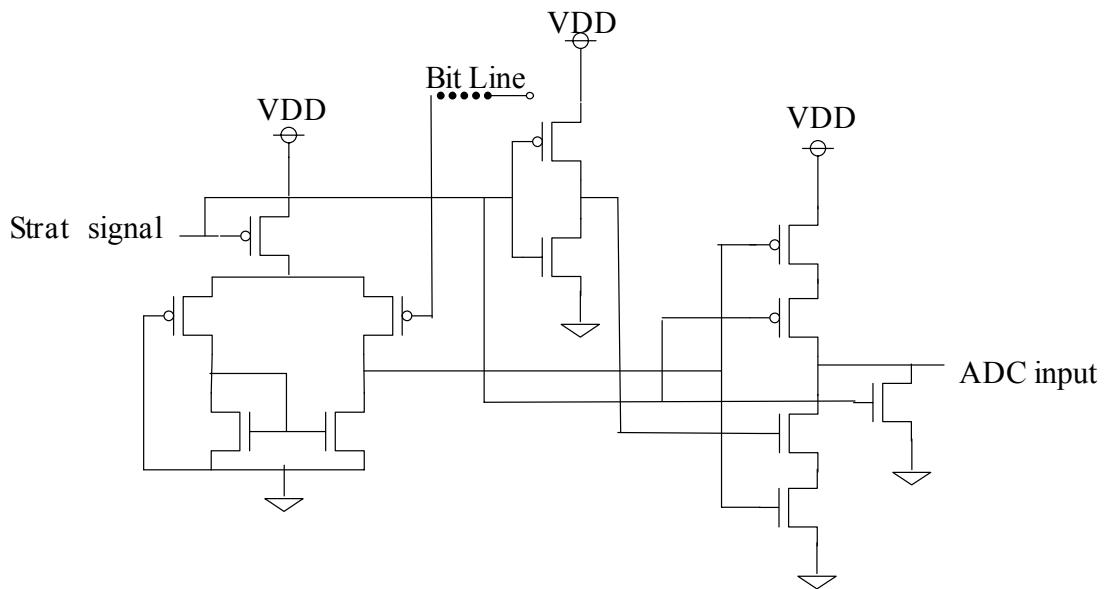

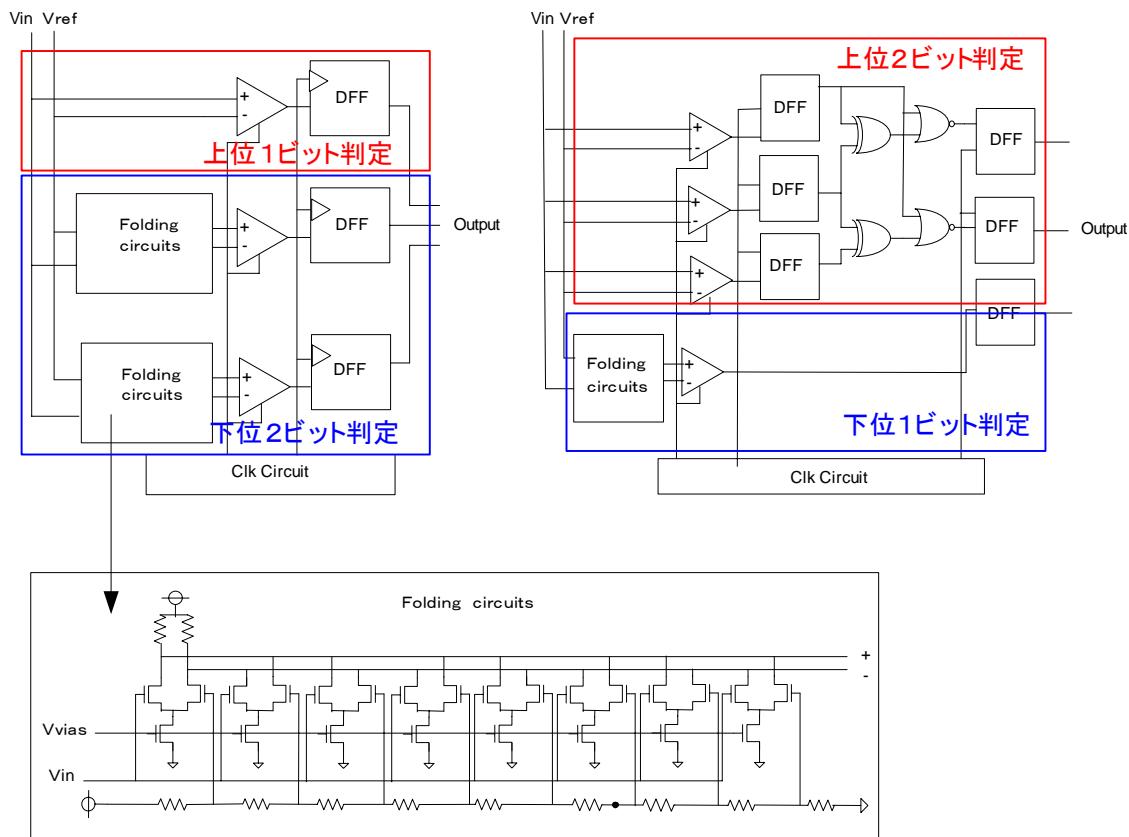

設計した線形増幅器回路を図 4-7に図に示す. この回路の動作は, 差動センスアンプの低電圧部の動作を利用して, 後段のクロックドインバータの閾値付近を入力として与えている. これにより特性の鈍ったインバータの特性を利用している. インバータの閾値部のS型の歪みを差動センスアンプの特性で打ち消している. 設計した線形増幅器回路の入出力特性を図 4-8に示す. 各素子抵抗値でのビット線の電圧と線形増幅後の電圧の結果を表 4-1示す. BIT線の電圧 0.3V-0.7Vをこの線形アンプにより, 1V-3Vまで増幅させていることが分かる.

図 4-7 線形増幅回路

図 4-8 線形増幅器の入出力特性

表 4-1 線形増幅器の結果

| 素子抵抗値( $\Omega$ ) | 論理値 | ビット線電圧(V) | 増幅後(V) |

|-------------------|-----|-----------|--------|

| 40.62K            | 111 | 834m      | 3.10   |

| 10.86K            | 110 | 734m      | 2.73   |

| 5.370K            | 101 | 629m      | 2.42   |

| 2.086K            | 100 | 470m      | 1.89   |

| 1.365K            | 011 | 404m      | 1.60   |

| 1.061K            | 010 | 372m      | 1.39   |

| 0.992K            | 001 | 352m      | 1.29   |

| 0.836K            | 000 | 344m      | 1.22   |

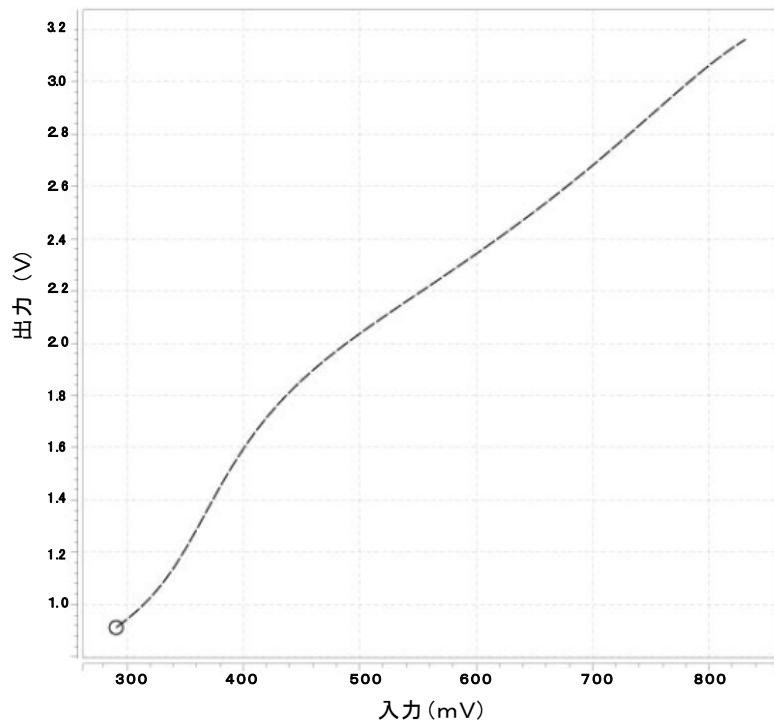

図 4-9 フォールディング型 ADC 回路図

表 4-2 ADC のシミュレーション結果

| 読み出し方法           |                                     | 読み出し時間(ns) | 面積(Tr 数) | 消費電流(mA) |

|------------------|-------------------------------------|------------|----------|----------|

| 3bit/cell ADC 方式 | Flash 型                             | 35         | 376      | 1.7      |

|                  | HalfFlash 型<br>上位 1 ビット             | 80         | 236      | 0.82     |

|                  |                                     |            |          |          |

|                  | HalfFlash 型<br>上位 2 ビット<br>下位 1 ビット | 80         | 234      | 1.12     |

|                  |                                     |            |          |          |

|                  |                                     |            |          |          |

|                  | Folding 型<br>上位 1 ビット<br>下位 2 ビット   | 43         | 158      | 0.93     |

|                  |                                     |            |          |          |

|                  |                                     |            |          |          |

|                  | Folding 型<br>上位 2 ビット<br>下位 1 ビット   | 50         | 214      | 1.08     |

|                  |                                     |            |          |          |

|                  |                                     |            |          |          |

| 1bit/cell センスアンプ | 差動センスアンプ                            | 20         | 13       | 0.32     |

### 4-3-3 シミュレーション

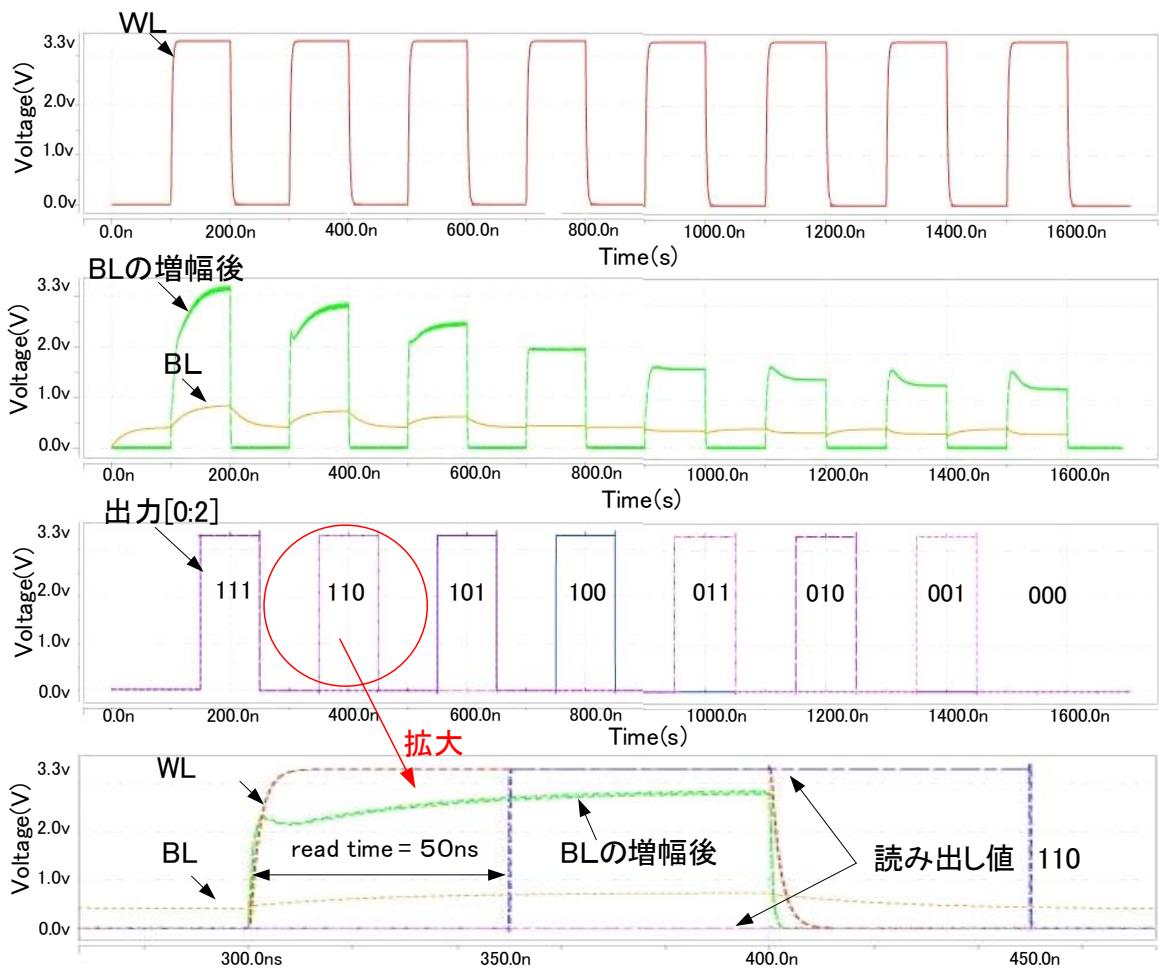

読み出し部全体のシミュレーション結果を図 4-10示す. 8 つの各素子の状態を読みだしできていることが確認できる. 読み出すメモリセルへのアクセスのためのデコーダ入力から 50nsでの読み出し時間で読み出しができることを確認した.

図 4-10 読み出し回路全体でのシミュレーション波形

#### 4-4 書き込み回路設計

##### 4-4-1 方式の検討

多値の書き込みの方法は図 4-11に示すように、2 つ考えられる。方法 1 は、書き込みを行う選択されたメモリセルにどんな値が格納されているかにかかわらず、一度リセット動作を行って素子を高抵抗状態にする。その後セット動作をデータ値分繰り返すことで、多値の書き込みを行う。方法 2 は、最初に選択されたセルの値の読み出し動作を行いセルに記憶している値を認識する。次にセルに記憶していた値と書き込む値を比較する。書き込む値の方が記憶している値よりも値より小さい場合は、SET動作だけを行い、逆に、書き込む値の方が記憶している値よりも値より大きい場合は一度リセット動作を行い、素子を高抵抗状態にしてからセット動作を書き込みたいデータ値分繰り返して、多値の書き込みを行う。この二つの方法を比べると前者の方は、制御は簡単であるが、無駄な書き込み動作が多く、書き込み時間と書き込みのサイクルも大きくなり、記憶素子の劣化を招く。従って、方法 2 の多値書き込み方式を採用した。

方法1 セルに書き込む値

|     | 000        | 001        | 010        | 011        | 100        | 101        | 110        | 111 |

|-----|------------|------------|------------|------------|------------|------------|------------|-----|

| 000 |            | R:1<br>S:6 | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 001 | R:1<br>S:7 |            | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 010 | R:1<br>S:7 | R:1<br>S:6 |            | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 011 | R:1<br>S:7 | R:1<br>S:6 | R:1<br>S:5 |            | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 100 | R:1<br>S:7 | R:1<br>S:6 | R:1<br>S:5 | R:1<br>S:4 |            | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 101 | R:1<br>S:7 | R:1<br>S:6 | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 |            | R:1<br>S:1 | R:1 |

| 110 | R:1<br>S:7 | R:1<br>S:6 | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 |            | R:1 |

| 111 | R:1<br>S:7 | R:1<br>S:6 | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 |     |

セルに記憶している値

方法2 セルに書き込む値

|     | 000 | 001        | 010        | 011        | 100        | 101        | 110        | 111 |

|-----|-----|------------|------------|------------|------------|------------|------------|-----|

| 000 |     | R:1<br>S:6 | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 001 | S:1 |            | R:1<br>S:5 | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 010 | S:2 | S:1        |            | R:1<br>S:4 | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 011 | S:3 | S:2        | S:1        |            | R:1<br>S:3 | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 100 | S:4 | S:3        | S:2        | S:1        |            | R:1<br>S:2 | R:1<br>S:1 | R:1 |

| 101 | S:5 | S:4        | S:3        | S:2        | S:1        |            | R:1<br>S:1 | R:1 |

| 110 | S:6 | S:5        | S:4        | S:3        | S:2        | S:1        |            | R:1 |

| 111 | S:7 | S:6        | S:5        | S:4        | S:3        | S:2        | S:1        |     |

セルに記憶している値

S : SETパルスの回数 R : RESETパルスの回数

図 4-11 多値の書き込み方法

#### 4-4-2 回路構成及び動作

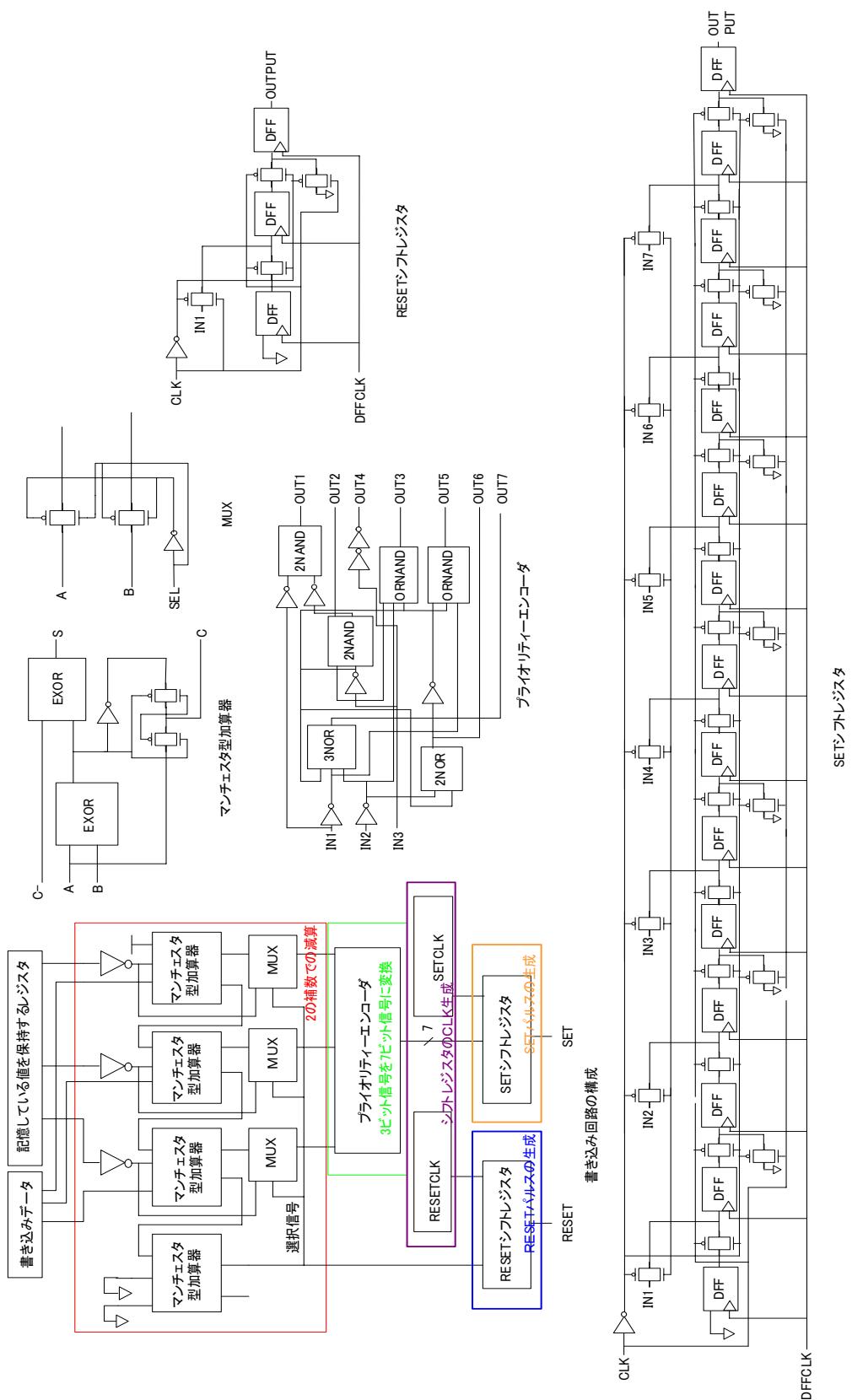

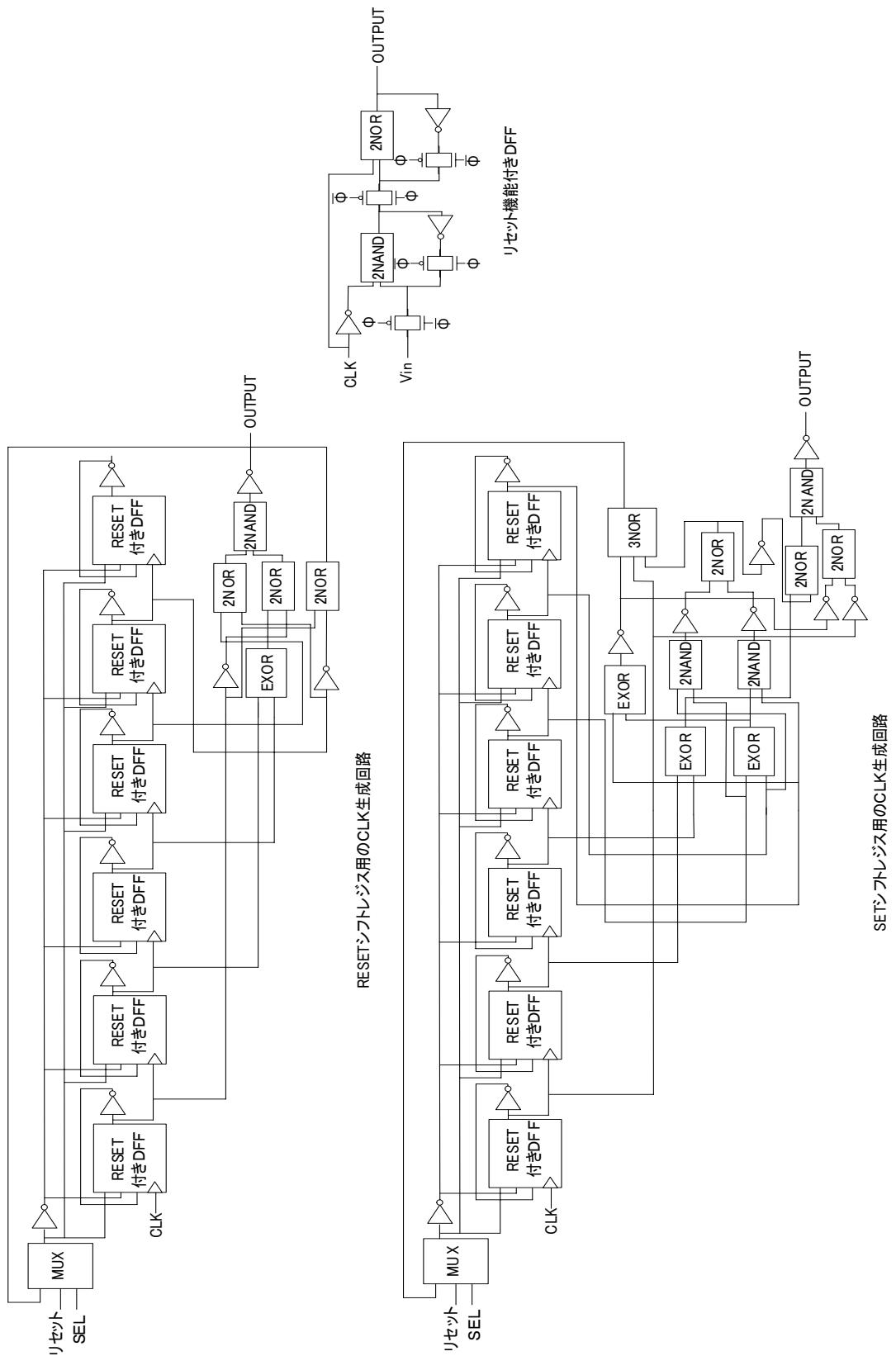

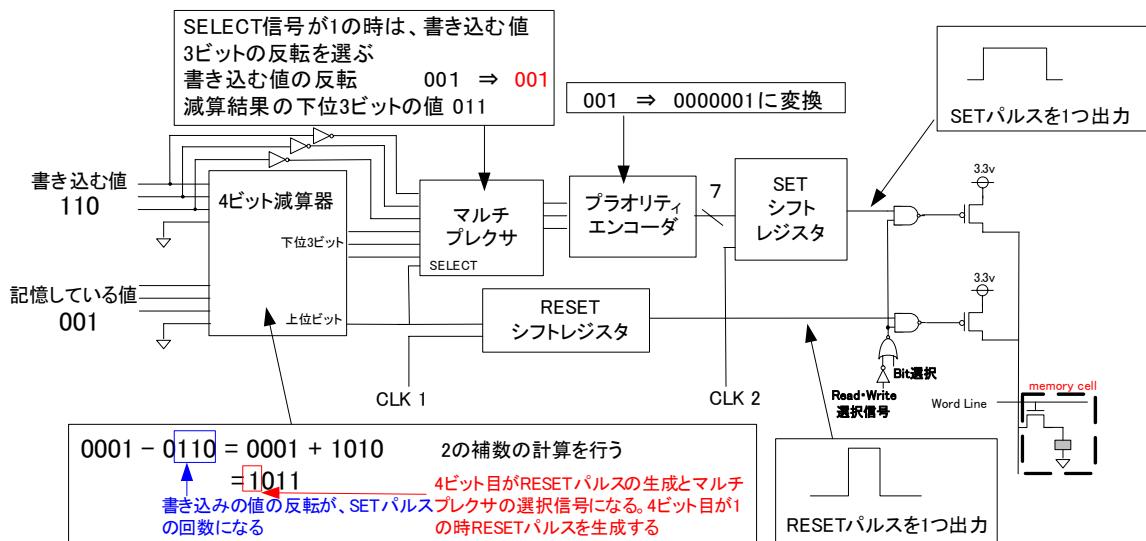

方法2を用いた書き込み回路のブロック図を図4-12に示す。さらに、図4-12、図4-13に詳細な回路を示す。減算器を用いてセルに書き込む値からセルに記憶している値を二の補数の計算を行い、SETとRESETのパルスを出すかの判別とSETパルスの回数を決める。減算器における入力の全パターンにおける出力結果を図4-14を示す。減算した結果の下位4ビット目の信号で、RESETを行うのかを判断する。書き込む値<記憶している値の書き込みの時は、必ず4ビット目の信号は0になり、(記憶している値)-(書き込む値)の下位3ビットの信号は、SETパルスの回数になる。よって、0の場合は、減算結果の下位3ビットの値を次のプライオリティエンコーダに入力する。逆に、書き込む値>記憶している値の書き込みの時は、必ず4ビット目の信号は1になり、書き込む値の反転を次のプライオリティエンコーダに入力する。プライオリティエンコーダで3ビット信号から7ビット信号に変換する。変換した信号をSETシフトレジスタに取り込み、SETパルスを生成する。またRESETパルスを生成する場合は、RESETのシフトレジスタに減算結果の4ビット目の信号を取り込み、4ビット目の信号が1の時はRESETパルスを生成する。SETシフトレジスタやRESETシフトレジスタのCLKを制御することで、パルスの幅やパルス生成の間隔を制御する。

図 4-12 書き込み回路の詳細図 1

図 4-13 書き込み回路の詳細図 2

| 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            | 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            |

|---------|-------|-----------------|-----------------------|------------------|---------|-------|-----------------|-----------------------|------------------|

| 0111    | 0000  | 111             | 10111                 | SET:7            | 0011    | 0000  | 111             | 10011                 | SET:3            |

|         | 0001  | 110             | 10110                 | SET:6            |         | 0001  | 110             | 10010                 | SET:2            |

|         | 0010  | 101             | 10101                 | SET:5            |         | 0010  | 101             | 10001                 | SET:1            |

|         | 0011  | 100             | 10100                 | SET:4            |         | 0011  | 100             | 10000                 | 0                |

|         | 0100  | 011             | 10011                 | SET:3            |         | 0100  | 011             | 01111                 | RESET:1<br>SET:3 |

|         | 0101  | 010             | 10010                 | SET:2            |         | 0101  | 010             | 01110                 | RESET:1<br>SET:2 |

|         | 0110  | 001             | 10001                 | SET:1            |         | 0110  | 001             | 01101                 | RESET:1<br>SET:1 |

|         | 0111  | 000             | 10000                 | 0                |         | 0111  | 000             | 01100                 | RESET:1          |

| 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            | 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            |

| 0110    | 0000  | 111             | 10110                 | SET:6            | 0010    | 0000  | 111             | 10010                 | SET:2            |

|         | 0001  | 110             | 10101                 | SET:5            |         | 0001  | 110             | 10001                 | SET:1            |

|         | 0010  | 101             | 10100                 | SET:4            |         | 0010  | 101             | 10000                 | 0                |

|         | 0011  | 100             | 10011                 | SET:3            |         | 0011  | 100             | 01111                 | RESET:1<br>SET:4 |

|         | 0100  | 011             | 10010                 | SET:2            |         | 0100  | 011             | 01110                 | RESET:1<br>SET:3 |

|         | 0101  | 010             | 10001                 | SET:1            |         | 0101  | 010             | 01101                 | RESET:1<br>SET:2 |

|         | 0110  | 001             | 10000                 | 0                |         | 0110  | 001             | 01100                 | RESET:1<br>SET:1 |

|         | 0111  | 000             | 01111                 | RESET:1          |         | 0111  | 000             | 01011                 | RESET:1          |

| 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            | 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            |

| 0101    | 0000  | 111             | 10110                 | SET:5            | 0001    | 0000  | 111             | 10001                 | SET:1            |

|         | 0001  | 110             | 10101                 | SET:4            |         | 0001  | 110             | 10000                 | 0                |

|         | 0010  | 101             | 10100                 | SET:3            |         | 0010  | 101             | 01111                 | RESET:1<br>SET:5 |

|         | 0011  | 100             | 10010                 | SET:2            |         | 0011  | 100             | 01110                 | RESET:1<br>SET:4 |

|         | 0100  | 011             | 10001                 | SET:1            |         | 0100  | 011             | 01101                 | RESET:1<br>SET:3 |

|         | 0101  | 010             | 10000                 | 0                |         | 0101  | 010             | 01100                 | RESET:1<br>SET:2 |

|         | 0110  | 001             | 01111                 | RESET:1<br>SET:1 |         | 0110  | 001             | 01011                 | RESET:1<br>SET:1 |

|         | 0111  | 000             | 01110                 | RESET:1          |         | 0111  | 000             | 01010                 | RESET:1          |

| 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            | 記憶している値 | 書き込む値 | 書き込む値<br>3ビット反転 | 書き込む値—記憶している値<br>減算結果 | パルス回数            |

| 0100    | 0000  | 111             | 10100                 | SET:4            | 0000    | 0000  | 111             | 10000                 | 0                |

|         | 0001  | 110             | 10011                 | SET:3            |         | 0001  | 110             | 01111                 | RESET:1<br>SET:6 |

|         | 0010  | 101             | 10010                 | SET:2            |         | 0010  | 101             | 01110                 | RESET:1<br>SET:5 |

|         | 0011  | 100             | 10001                 | SET:1            |         | 0011  | 100             | 01101                 | RESET:1<br>SET:4 |

|         | 0100  | 011             | 10000                 | 0                |         | 0100  | 011             | 01100                 | RESET:1<br>SET:3 |

|         | 0101  | 010             | 01111                 | RESET:1<br>SET:2 |         | 0101  | 010             | 01011                 | RESET:1<br>SET:2 |

|         | 0110  | 001             | 01110                 | RESET:1<br>SET:1 |         | 0110  | 001             | 01010                 | RESET:1<br>SET:1 |

|         | 0111  | 000             | 01101                 | RESET:1          |         | 0111  | 000             | 01001                 | RESET:1          |

図 4-14 減算回路の全パターン

### 4-4-3 書き込み動作

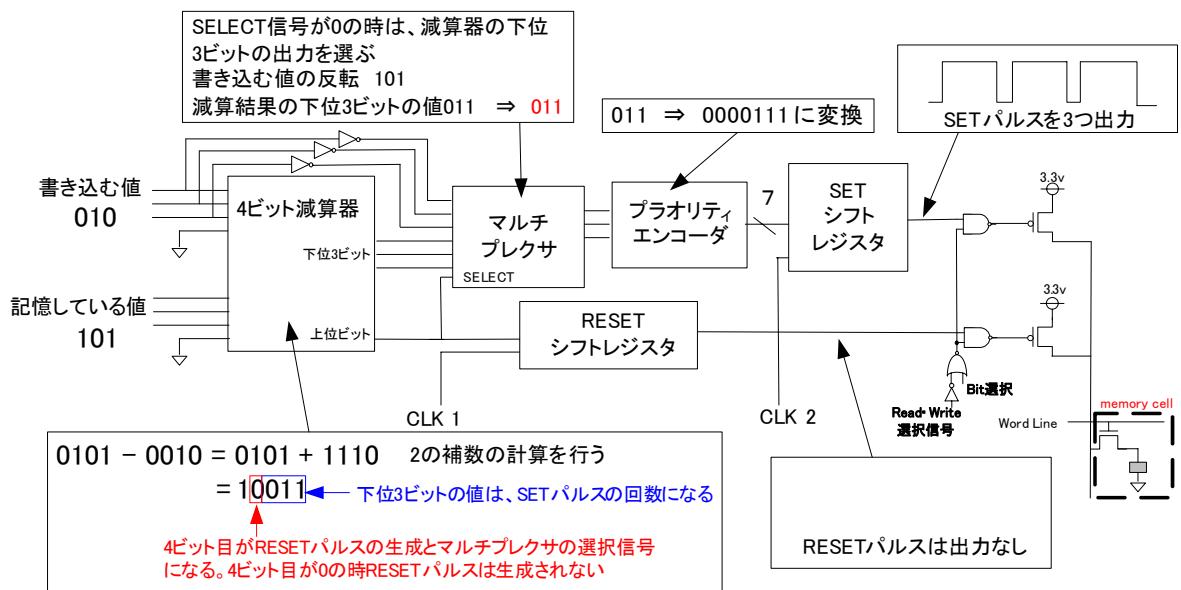

#### 書き込む値 < 記憶している値の書き込み動作の場合

書き込む論理値が記憶している論理値よりも小さい場合は、SETパルスのみを生成すればよい書き込みである。例として書き込み値が 010 で記憶している値が 101 の時を図 4-15 に示す。まず、減算器で記憶している論理値から書き込む論理値を 2 の補数で減算をする。この場合の補数計算によって得られる出力の 4 ビット目の信号は必ず 0 になる。この信号が 0 の時は RESET パルス生成しないという信号になる。よって RESET シフトレジスタに 0 が入力され RESET パルスは生成されない。またこの 4 ビット目の信号は、マルチプレクサの選択信号になる。0 の場合は、減算器の出力の下位 3 ビットをマルチプレクサの出力になる。よって下位 3 ビットの値がプライオリティエンコーダに入力される。プライオリティエンコーダで例では、 $011 \Rightarrow 0000111$  に変換される。プライオリティエンコーダで 3 ビット信号から 7 ビット信号に変換する。変換された信号をシフトレジスタに取り込み、SET パルス 3 つ生成している。

図 4-15 書き込む値 < 記憶している値の書き込み動作

#### 書き込む値 > 記憶している値の書き込み動作の場合

書き込む論理値が記憶している論理値よりも大きい場合は、RESET パルスと SET パルスを生成すればよい書き込みである。例として書き込み値が 110 で記憶している値が 001 の時を図 4-16

に示す。まず減算器で記憶している論理値から書き込む論理値を 2 の補数で減算する。この場合の補数計算によって得られる出力の 4 ビット目の信号は必ず 1 になる。この信号が 1 の時はRESET パルス生成するという信号になる。よってRESETシフトレジスタに 1 が入力されRESETパルスが 1 つ生成される。またこの 4 ビット目の信号は、マルチプレクサの選択信号になる。1 の場合は、書き込む値の反転した値をマルチプレクサで選択して、出力となる。よって書き込む値の反転した値がプライオリティエンコーダに入力される。プライオリティエンコーダで例では、 $001 \Rightarrow 0000001$  に変換される。プライオリティエンコーダで 3 ビット信号から 7 ビット信号に変換する。変換された信号をシフトレジスタに取り込み、SETパルス 1 つを生成する。

図 4-16 書き込む値>記憶している値の書き込み動作

#### 4-4-4 シミュレーション

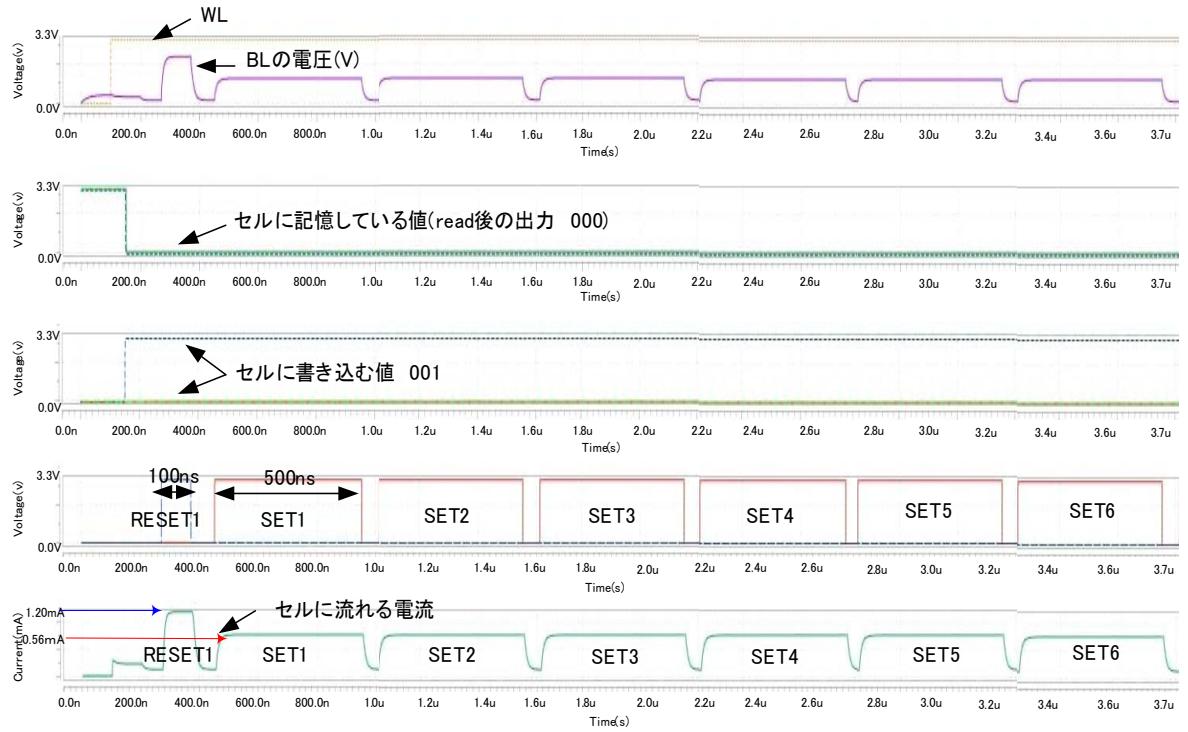

書き込み回路のシミュレーションの結果を図 4-17 に示す。例として、セルに記憶している値が 000 でセルに書き込む値を 001 と仮定した場合を示している。まず、セルの記憶している値を読み出し動作を行いレジスタに格納する。例の場合、セルに記憶している値が 000 と認識する。次に書き込み回路によって記憶している値と書き込む値を比べる。その結果 RESETパルス  $\times 1$  とSETパルス  $\times 6$  が生成される。その電圧パルスを電流パルスに変換してメモリセルに流し書き込みを行っていることが確認できる。最大の書き込み時間と最大の電流消費の書き込みは、SETパルスを 7 回書き込む場合で、4.2us で  $560\mu\text{A} \times 500\text{ns} \times 7$  回になる。

図 4-17 書き込み動作シミュレーション波形

設計した 3bit/cell の多値記憶のシミュレーション結果を表 4-3 にまとめる。同じ素子を用いた 2 値の相変化メモリとの比較結果を

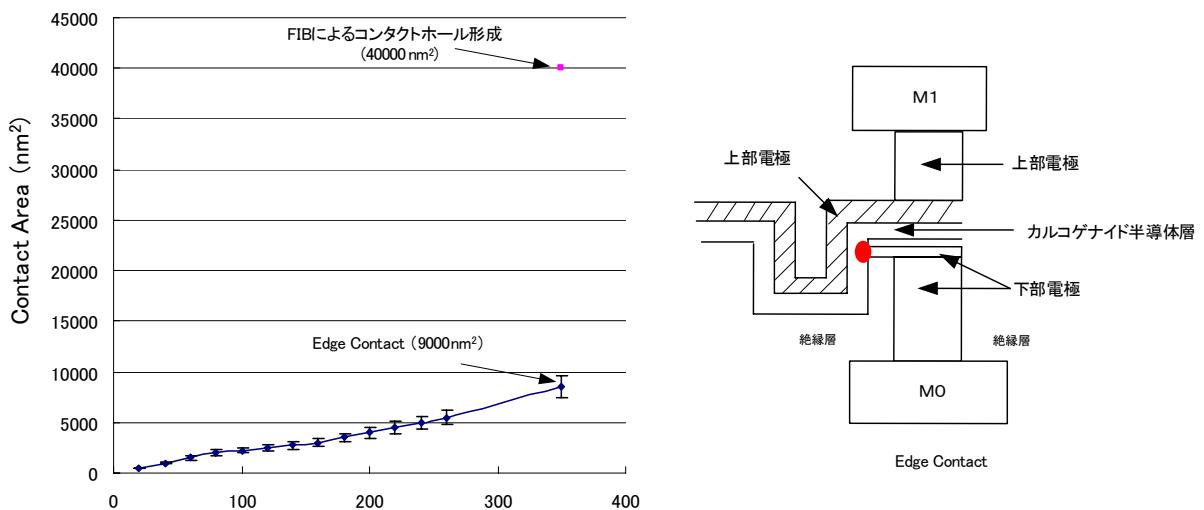

表 4-4 にまとめる。比較を行うと多値化によって記憶密度は、3 倍で向上している。読み出し時間や最小の書き込み時間と最小の書き込みの消費電流については、あまり差がない。しかし、書き込み時間と最大の書き込みの消費電流は、大きく差がある。しかし、書き込み消費電流については、素子領域を小さくすることで、削減できる。例えば Samsung 社のエッジコンタクトによるカルコゲナイト半導体層の接続方法を用いれば、0.35um プロセスを用いていても 9000nm<sup>2</sup> の素子領域まで小さくすることができる。SeSbTe の電流密度から計算すると、一回の RESET 電流は、270uA、一回の SET 電流は、126uA と書き込み電流を uA オーダーまで小さくすることが可能になる。また、書き込みの電流値が小さくなることで、メモリセルのアクセスもトランジスタのサイズも小さくすることができるためメモリセル面積も小さくなる。

表 4-5 に比較した結果を示す。素子領域を小さくすることで全体の書き込みでの消費電流を小さくできる。また書き込み電流の削減より、メモリセルの密度を小さくすることができるため、より高密

度なメモリの実現の可能性がある。

表 4-3 シミュレーション結果のまとめ

|            |                                                                          |

|------------|--------------------------------------------------------------------------|

| プロセス       | CMOS0.35um Metal 3 層                                                     |

| 電源電圧       | 3.3V                                                                     |

| メモリセル規模    | 512 × 1024                                                               |

| 記憶素子/加工サイズ | Se <sub>15</sub> Sb <sub>15</sub> Te <sub>70</sub> / 0.04um <sup>2</sup> |

| セルサイズ/記憶密度 | 13.34um <sup>2</sup> /3bit/cell 36F <sup>2</sup> /bit                    |

| 読み出し時間     | 50ns                                                                     |

| 書き込み時間     | 4.2us                                                                    |

| 読み出し消費電流   | 2.83mA @5MHz                                                             |

| 書き込みの消費電流  | 1.605mA @4.2us SET×7                                                     |

表 4-4 2 値相変化メモリとの比較

| 項目            | 1bit/cell×3bit                                          | 3bit/cell 本方式                                          |

|---------------|---------------------------------------------------------|--------------------------------------------------------|

| セルサイズ/記憶密度    | 13.34um <sup>2</sup> /1bit/cell(104F <sup>2</sup> /bit) | 13.34um <sup>2</sup> /3bit/cell(36F <sup>2</sup> /bit) |

| 読み出し時間        | 27ns                                                    | 50ns                                                   |

| 書き込み時間(最大)    | 500ns                                                   | 4.2us                                                  |

| 書き込むパルス回数(最大) | SET×1                                                   | SET×7                                                  |

| 最大の読み出し消費電流   | 4.093mA @5MHz                                           | 4.661mA @5MHz                                          |

| 最大の書き込み消費電流   | 4.343mA @500ns SET×3bit                                 | 1.605mA @4.2us SET×7                                   |

図 4-18 エッジコンタクト方式における素子領域

表 4-5 書き込み消費電流の削減の例

|                | 素子領域                | 1bit/cell×3bit                                | 3bit/cell 本方式                                |

|----------------|---------------------|-----------------------------------------------|----------------------------------------------|

| 最大書き込み<br>消費電流 | 0.2um×0.2um         | 4.343mA                                       | 1.605mA                                      |

|                | 9000nm <sup>2</sup> | 3.048mA                                       | 1.291mA                                      |

| 面積             | 0.2um×0.2um         | 13.34um <sup>2</sup> (109F <sup>2</sup> /bit) | 13.34um <sup>2</sup> (36F <sup>2</sup> /bit) |

|                | 9000nm <sup>2</sup> | 7.935um <sup>2</sup> (65F <sup>2</sup> /bit)  | 7.935um <sup>2</sup> (22F <sup>2</sup> /bit) |

## 4-5 結言

この章では、実験で観測されたデータを基に、PRAMの基本構成である2値メモリ回路を拡張し、多値メモリ回路を提案した。回路実装において、書き込み時には、予め書き込み先のデータを読み出し、書き込みデータ比較することで、消費電力を低減するアーキテクチャを提案した。読み取り動作を行った所、100MHz 読み出しサイクルにおいて、3nsec 以内の読み出し速度を得ることができた。(エンコーダ方式)

## 第5章 PNSRAM

### 5-1 背景

ここでは、PNSRAM アーキテクチャを提案するに至った背景について述べる。

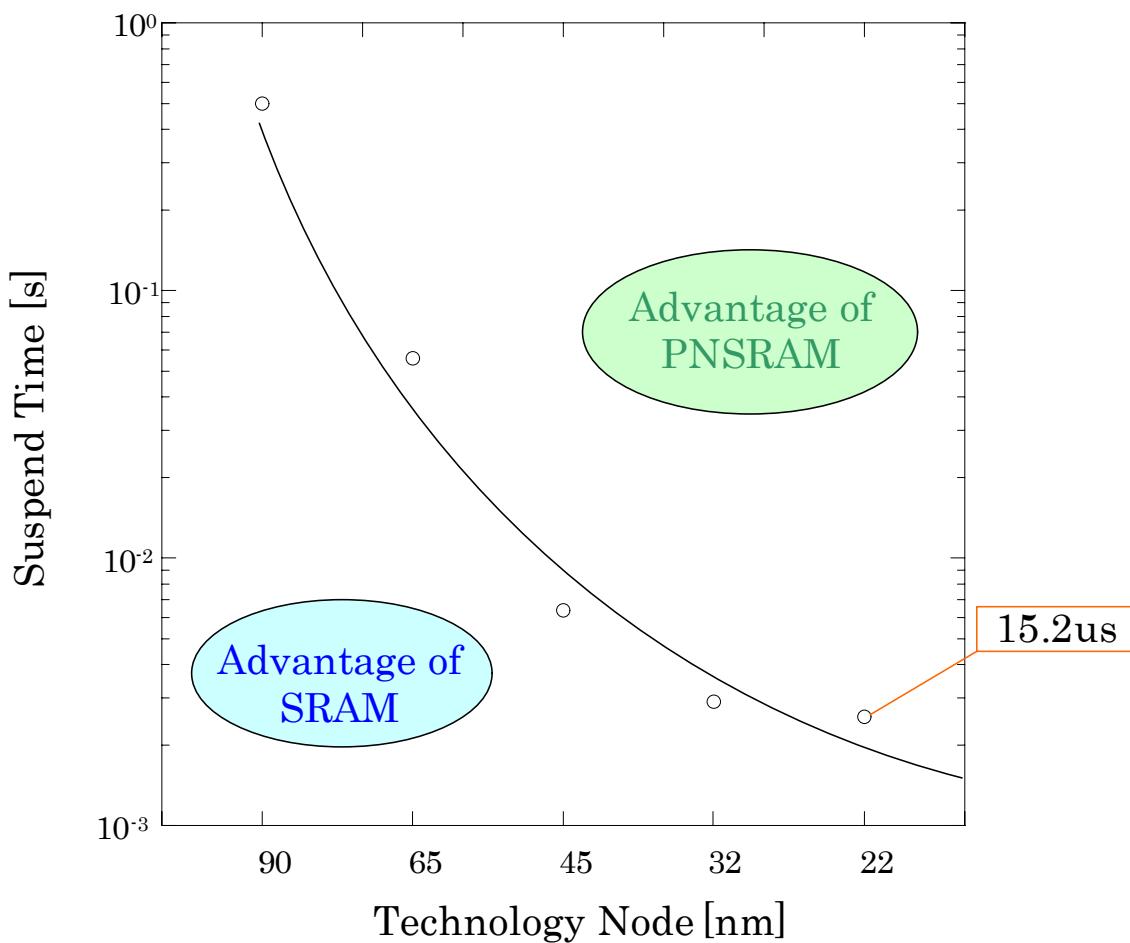

図 5-1 SoC における LOP, LSTP の動的／静的消費電力

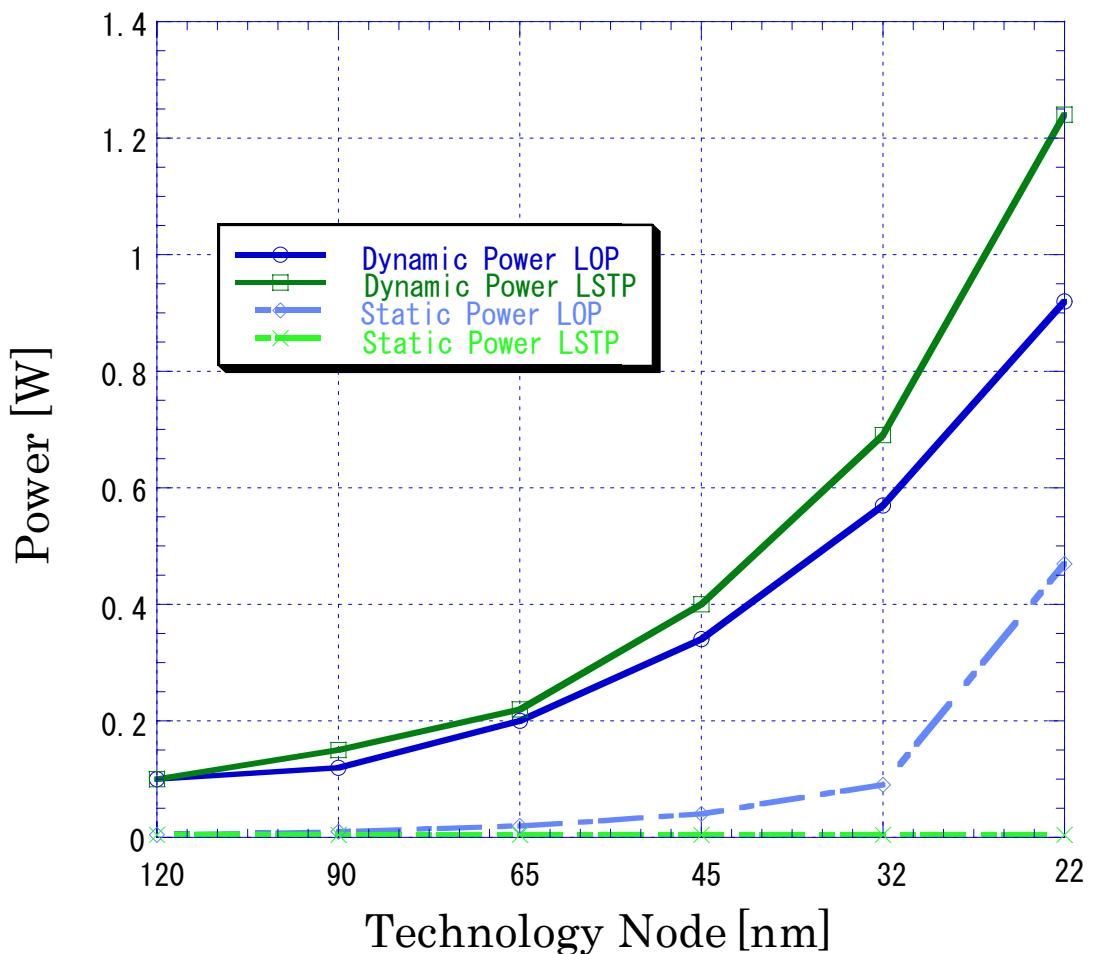

図 5-1にSoCにおけるLOP, LSTPのそれぞれに対する、動的・静的消費電力を示す。横軸がTechnology Node、縦軸が消費電力である。図 5-1は図 1-4のLOP, LSTPのパワーギャップを実際の値で書き示している。図 1-4ではLOPの静的消費電力の問題について言及したが、LSTPはLOPに比べ、物性自体を書き換えるため、動作消費電力がLOPより高くなる欠点を有する。

他の不揮発性メモリに比べ、利点の多い PRAM であるが、電気的に書き換えが可能な

SRAM に比べ、以下のような欠点を有している。

- a) 記録材料の状態を書き換えの度に変化させている為に、主に書き込み動作に遅延を生じる

- b) データの書き換えにより記録材料の疲労が生じ、書き換え回数が制限される

- c) 書き換え時の消費電力が大きい

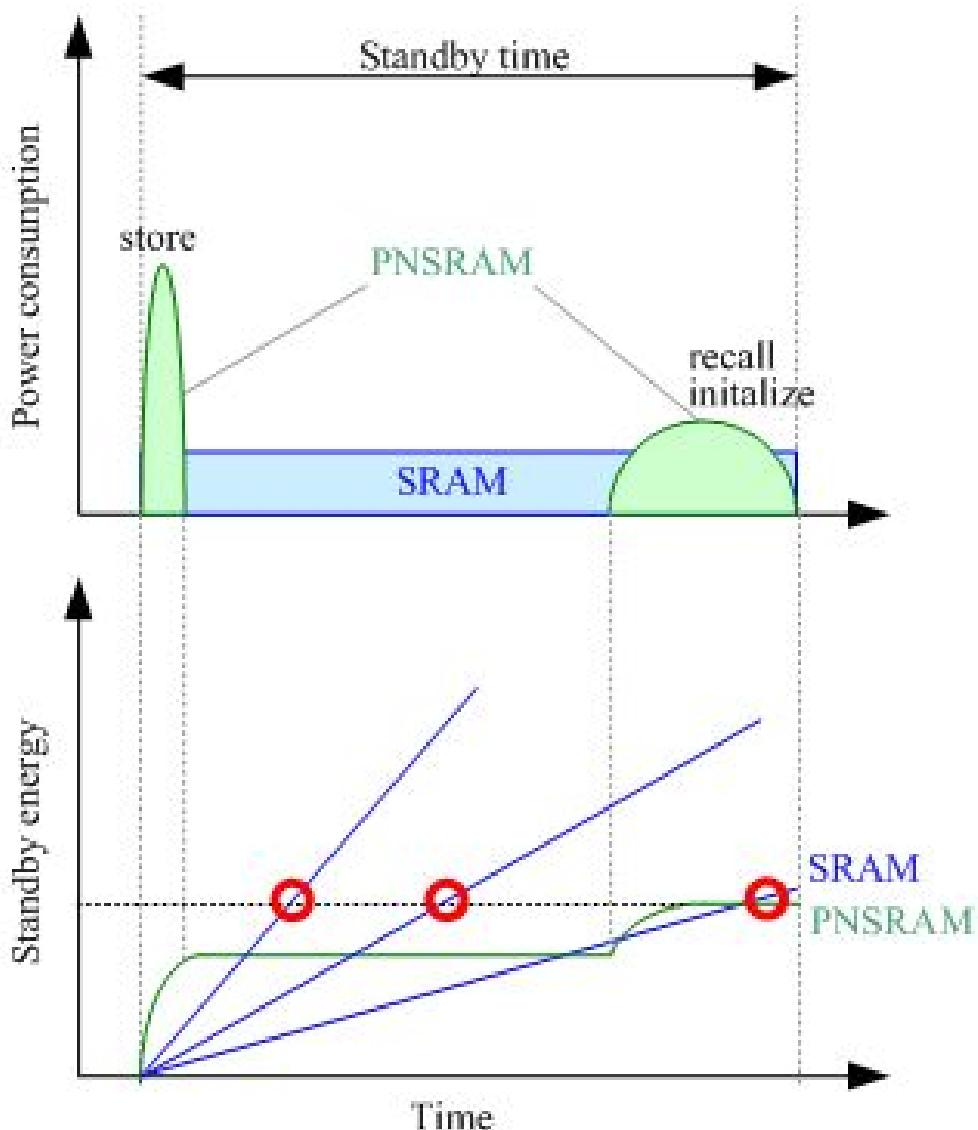

そこで、常に状態を書き換え、不揮発性を維持しなくとも、待機モードに至る直前や、電源を落とす時にのみ、記録材料にバックアップを行うことで前述の欠点を克服できる方法を考え、従来の SRAM 構造に、PRAM に用いられる相変化材料による不揮発データの保持を可能とする構造を加えた不揮発性 SRAM(以下、PNSRAM : Phase-change nonvolatile SRAM)を提案する。

PNSRAM では、上記の問題を以下のように改善している。

- a) 通常動作時は SRAM として揮発性書き込みを行う。その為、不揮発性物質の状態遷移時間による律速から解放され、高速化できる

- b) 待機時、または電源終了時の不揮発部への書き込みを行うため、揮発性及び不揮発性の書き込みシーケンスを分離し、不揮発性物質への書き込む機会を減らすことで疲労を抑えることが出来、事実上書き換え無制限を実現可能とした。

- c) 待機時及び、スタンバイ時には電源供給を止めることで SRAM の待機電力を改善し、また、動作時には、揮発性動作を行うことにより PRAM の動作電力も共に改善

そこで、常に状態を書き換え、不揮発性を維持しなくとも、待機モードに至る直前や、電源を落とす時に記録材料にバックアップを行うことで実用性に耐えうるのではないかと考え、従来のSRAM構造に、PRAMに用いられる相変化材料による不揮発データの保持を可能とする構造を加えた不揮発性SRAM(以下、PNSRAM : Phase-change nonvolatile SRAM)を提案する。PNSRAMの消費電力は図 5-2に示すようにLOPの動作消費電力とLSTPの動作消費電力を併せ持つ仕様を持つ。

図 5-2 PNSRAM の消費電力予測

図 5-3 相変化動作の対応

PNSRAM では、既存のメモリ素子とは異なる動作方法をとっている。

これに習い、前章までで定義していたカルコゲナイト半導体の状態遷移動作を、PNSRAM の動作に対応させると、非晶質状態からの結晶状態の状態遷移制御（セット動作）を“初期化”，その逆操作（リセット動作）を“ストア”と定義する。（図 5-3参照）

以下では、相変化素子への影響を十分に考慮し作成したメモリアーキテクチャを、メモリ動作に沿いながら述べていく。

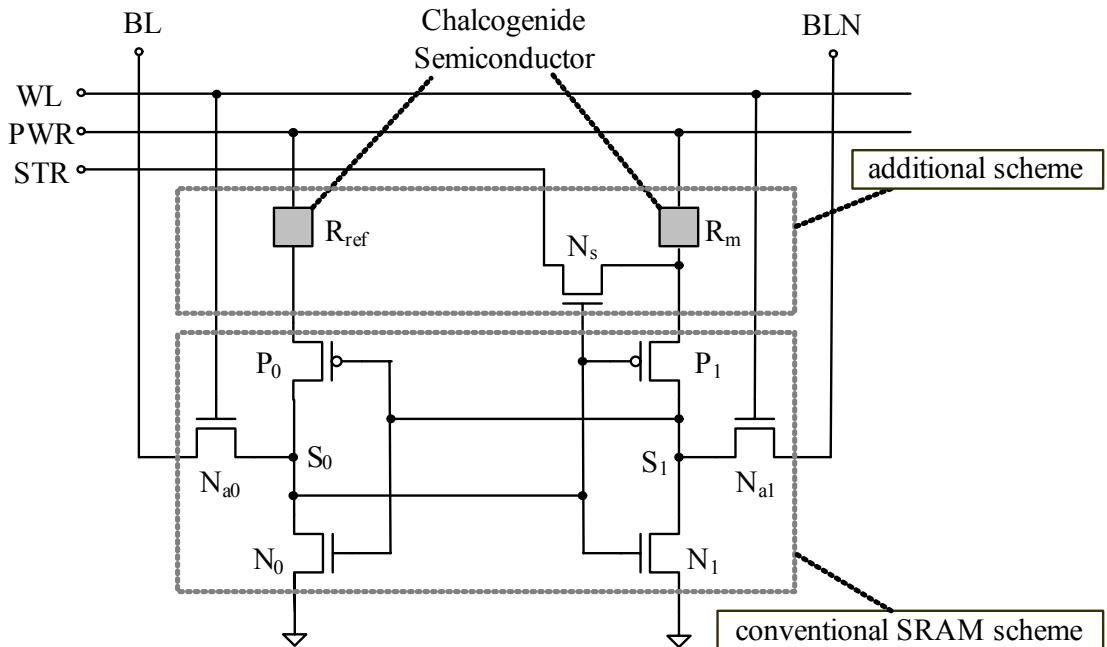

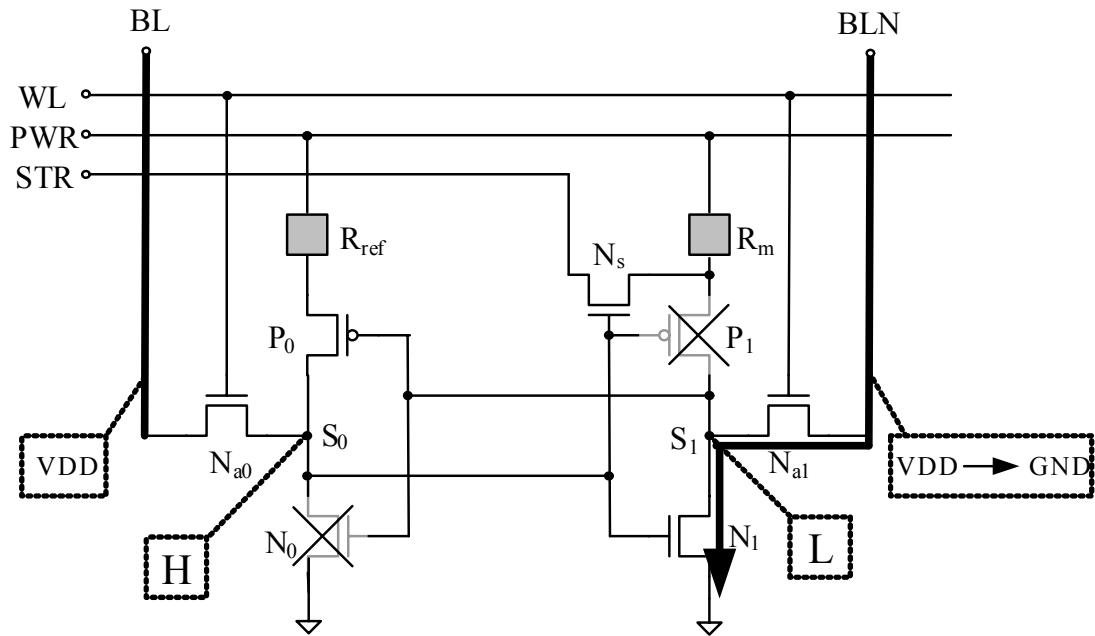

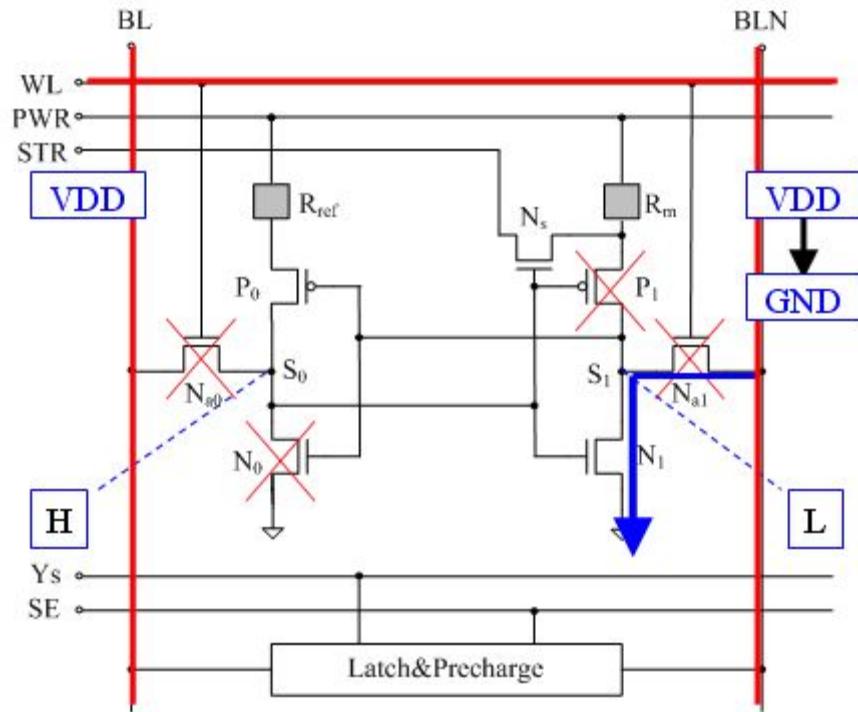

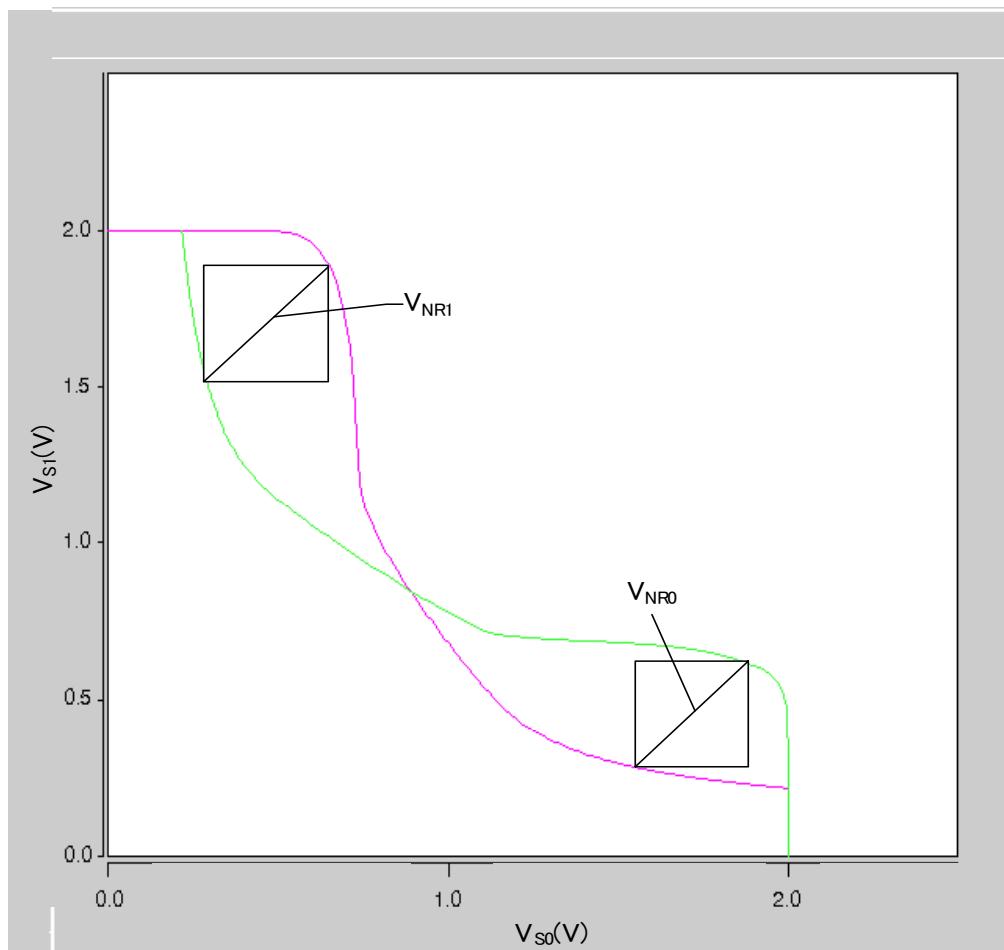

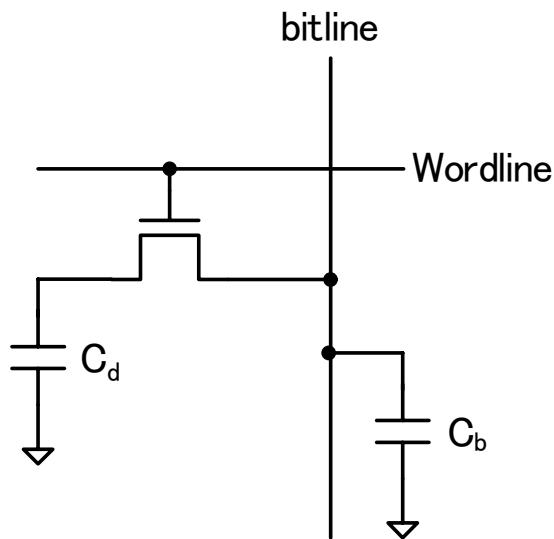

## 5-2 メモリセル構造

図 5-4にPNSRAMのメモリセル回路図を示す。従来の 6 トランジスタのSRAMメモリセルに 1 個のトランジスタ( $N_s$ )と 2 つのカルコゲナイト半導体素子( $R_{ref}$ および $R_m$ )と不揮発書き込み制御線STRを付加した構成となっている。 $R_{ref}$ はPoly-Si等の抵抗でも置き換えることは可能であるが、 $R_m$ を作成したときの膜の組成（バラツキ）に追随するために、カルコゲナイト半導体素子を用いている。これらの追加回路は電源線であるPWRとSRAMメモリセルの間に構成される（図 5-5）。信号線PWRは、本メモリセルの電源線である。信号線STRは、通常HIGHに保たれており、不揮発性書き込みを行う時に通電し書き換えを行う。

図 5-4 PNSRAM メモリセル

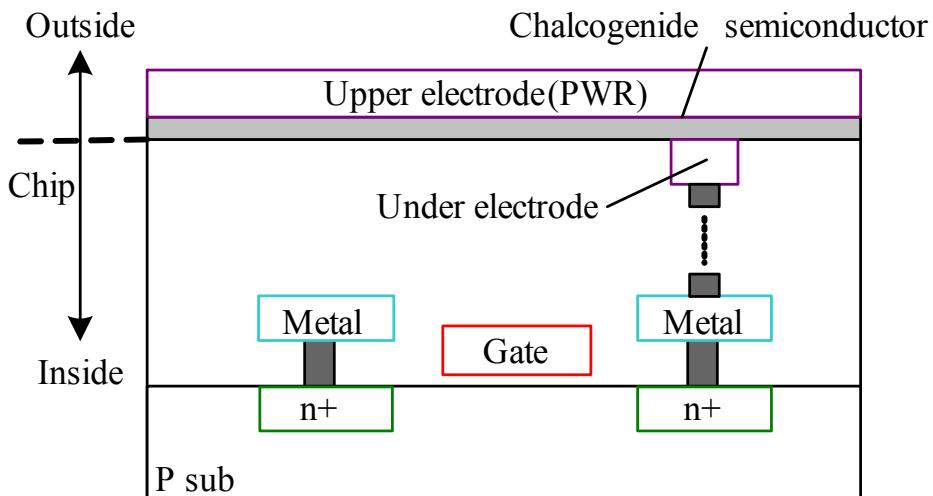

図 5-5に図 5-4におけるトランジスタ $N_s$ のメモリセル断面図を示す。ここでは 0.18um CMOSプロセス・5 層メタルを利用し、回路設計を行った。トランジスタ $P_0$ ( $P_1$ も同様)のソース側から 5 層の配線層を通じ、メモリセル真上に配置される記録層に接続される構造となっている。記録素子の相変化は、各メモリセル上部電極と隣接するカルコゲナイト半導体層の近傍のみで生じる為、マスクパターンを用いずに、上記 2 層をメモリセル全体で共有する。

図 5-5 トランジスタ(Ns)の断面図

### 5-3 メモリセル動作

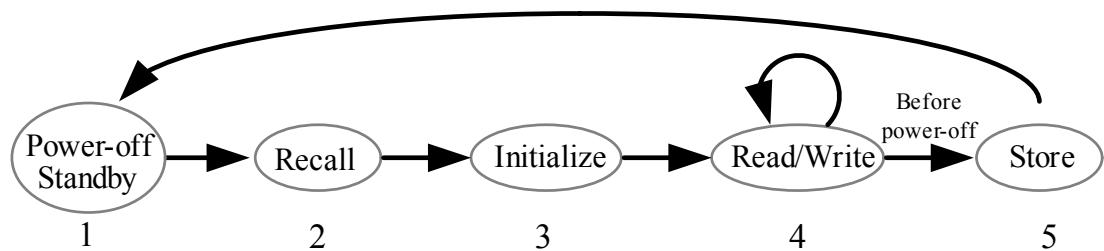

図 5-6 動作フロー

表 5-1 各信号線電位の変動

| Mode       | PWR       | BL / BLN          | WL  | STR                                       |

|------------|-----------|-------------------|-----|-------------------------------------------|

| Standby    | VDD → GND | GND               | GND | GND                                       |

| Recall     | GND → VDD | Pre-charged       | GND | GND → VDD                                 |

| Initialize | VDD       | Pre-charged       | GND | VDD → $V_{init}$ → VDD                    |

| Read/Write | VDD       | Read/Program Data | VDD | VDD                                       |

| Store      | VDD       | Pre-charged       | GND | $VDD \rightarrow V_{str} \rightarrow VDD$ |

図 5-6にPNSRAMメモリセルの諸動作を、表 5-1に各信号線電位の変動を示す。PNSRAMメモリセル動作順序および動作の概略を以下に示す。

1) スタンバイ／電源オフ：

SRAM が動作を必要としない場合、完全に電源を落とすことが可能である（デー

タは不揮発である相変化材料に記録される.

2) リコール :

電源投入時にカルコゲナイト半導体素子に保持されているデータを読み出す動作.

必ず行われる.

3) 初期化 :

リコールされた直後に必ず行われる動作. 記録材料の状態を初期化(低抵抗化)

する.

4) 読み出し／書き込み :

通常の SRAM 動作. 初期化が行われた後, 可能となる. この状態の時, 通常のメ

モリと同様に扱うことが出来る.

5) ストア :

カルコゲナイト半導体素子に, 現在メモリセルに保持されている論理値を書き込

む動作. 電源切断直前, 又は待機モードへの移行直前に必ず行う.

### 5-3-1 電源オフ／スタンバイ動作

電源オフ／スタンバイ動作時, メモリセルの電源線である PWR は GND 電位となる. デ

ータは不揮発部に格納されているため, データ保持のためのエネルギーは不要である. こ

の後, 次のリコール動作を経て, メモリセルが動作を始める.

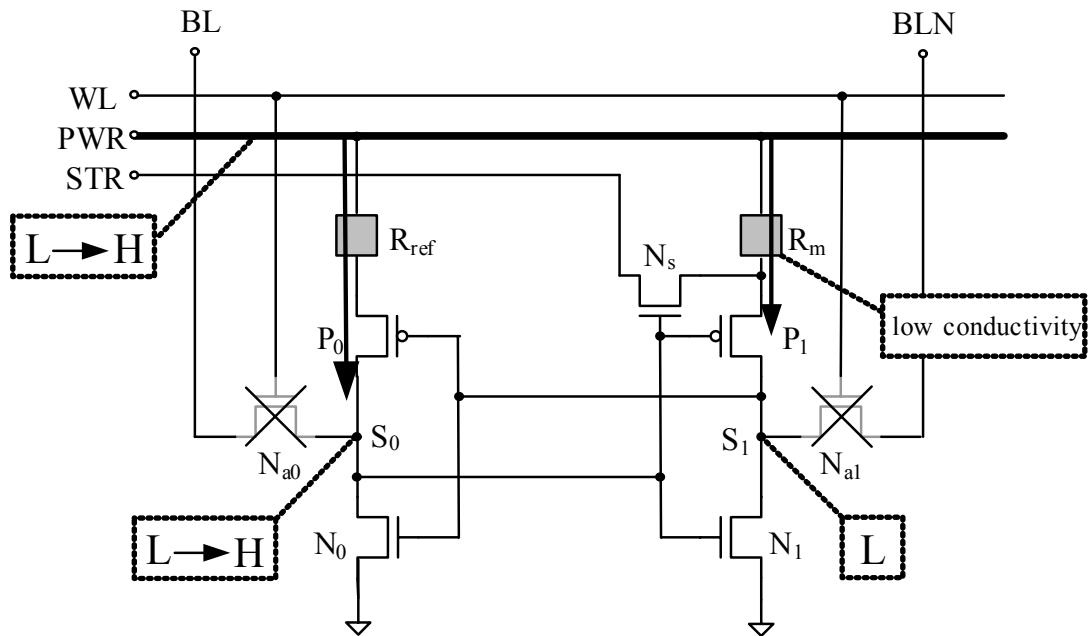

### 5-3-2 リコール動作

図 5-7にリコール動作時のメモリセルの様子を示す. 各メモリセルには二つの相変化素

子が接続されている. ここで, 左側の素子を参照抵抗 $R_{ref}$ とし, 右側の素子を記憶抵抗 $R_m$ と

定める. この時,  $R_m$ が高抵抗の非晶質状態ならば論理値 1 が保持されているとし, 低抵抗

の結晶状態であるならば論理値 0 が保持されていると規定する. また,  $R_{ref}$ は予め,  $R_m$ の抵

抗変化ステップの中間値を取るように調整しておくものとする.

図 5-7 リコール動作

リコール動作は次の流れで行われる。

- 1) 電源線PWRを電源電圧へチャージすることにより、メモリ回路へ電源供給する。この時、ワード線WLは接地電位であり、アクセストランジスタNa0, Na1はOFF状態である。これにより、メモリセルのインバータループ部へPWRから電流が流れこむ(図 5-7参照)。この時、トランジスタP0, P1それぞれに流れる電流はRref及びRmの抵抗値に依存する。

- 2) 仮に、Rmが高抵抗状態 (抵抗値は $R_m > R_{ref}$ ) であるとすると、P0側に比べ、P1側の電流が減少してしまい、S0とS1の電位は、比較してS0が高く、S1が低くなる。このため、P0 : オン, P1 : オフ, N0:オン, N1 : オフ, の傾向となり、それがインバータループによって增幅され、安定状態となり、論理値 1(S0 : H, S1 : L)となる。

以上の過程を経て、素子に保持されている状態をメモリセル中のSRAM部に読み出すことが出来る。一方で、Rmが低抵抗状態ならば、P1に大きな電流が流れ、S0の電位が低く、S1が高くなって安定状態となり論理値 0(S0 : L, S1 : H)が呼び出される。

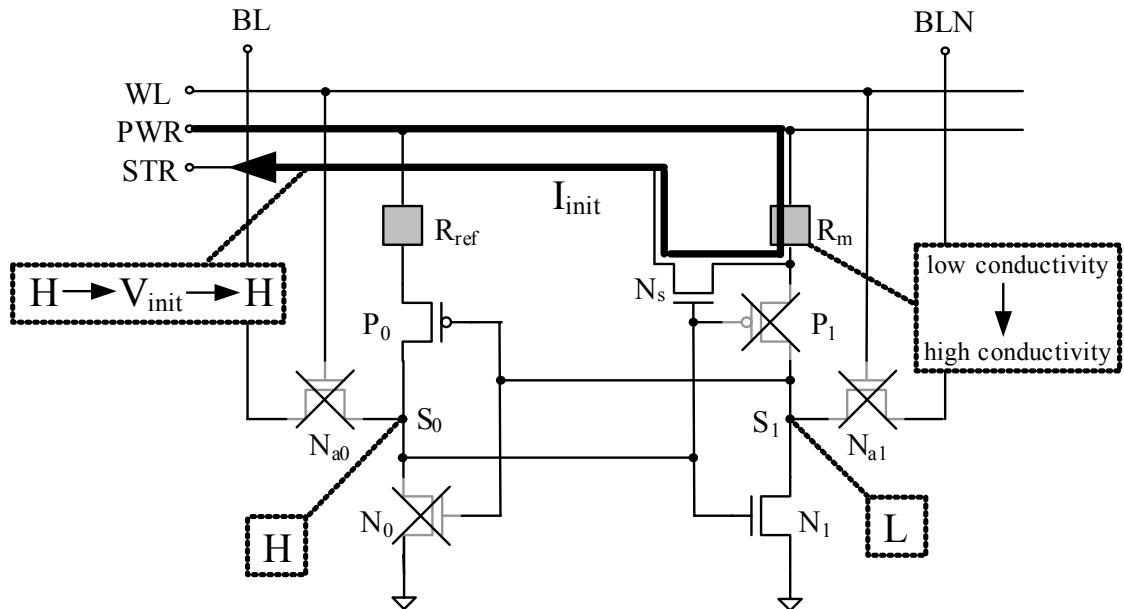

### 5-3-3 初期化動作

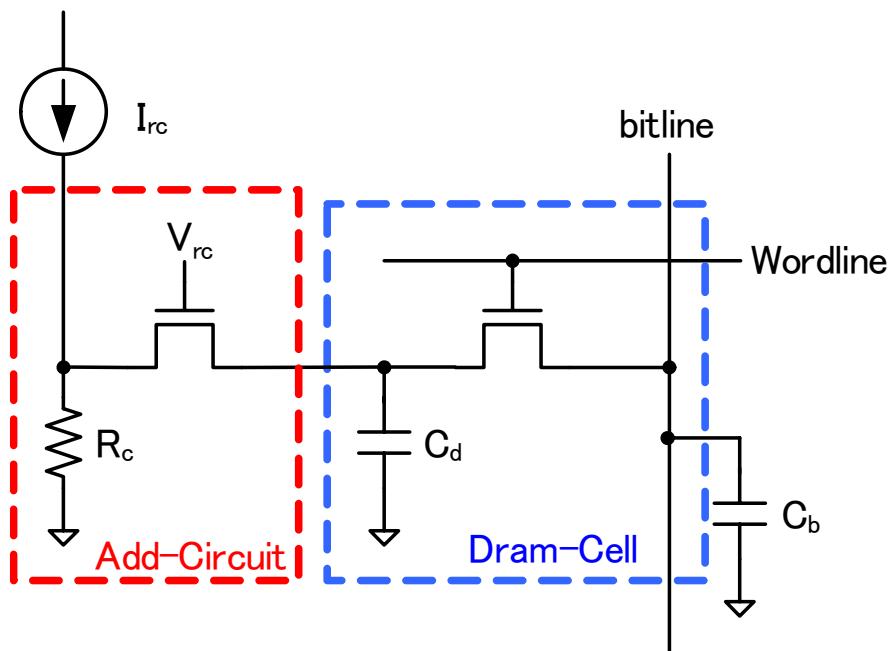

図 5-8に初期化動作時のメモリセル動作を示す。前述のリコール動作によってメモリセルに論理値 1 が誘起された全てのセルは素子Rmの状態は高抵抗状態である。ここで、デー

タを読み出した素子の状態をリセット、つまり、低抵抗状態へ遷移させる。この動作を行うことで、この後に行われるSRAM動作時の読み取り／書き込み動作への影響を抑える効果もある。

図 5-8 初期化動作

初期化動作は次の流れで行われる。

- 1) リコール動作後に論理値 1( $S_0 : H, S_1 : L$ )が呼び出されたメモリセルにおいて、トランジスタ $N_s$ はオン、 $P_1$ はオフとなっている。ここで、不揮発書き込み制御線STRを低電圧 $V_{init}$ に引き下げる。これにより、 $R_m$ のみに電流が流れる。(図 5-8参照)

- 2) この後、制御線STRを電源電圧へ引き上げる。結晶時間の間、STRを低電圧 $V_{init}$ に引き下げることによって、 $R_m$ が結晶化への条件を満たし、高抵抗状態から低抵抗状態に遷移する。

また、論理値 0( $S_0 : L, S_1 : H$ )が呼び出されたメモリセルでは、 $N_s$ はオフである為、STR線の電圧が変化しても、 $R_m$ に電流が流れることは無い。これによって、無駄な書き込み動作が抑えられ、50%の消費電力削減効果がある。このように、初期化動作はメモリセルの状態によって自動的に決定され、全セル同時に判定し動作することも可能である。しかし、実際はメモリ容量に依り、メモリ回路全体に通電させることは、電流量の関係から不可能であるため、メモリブロック毎に時分割して動作させる。

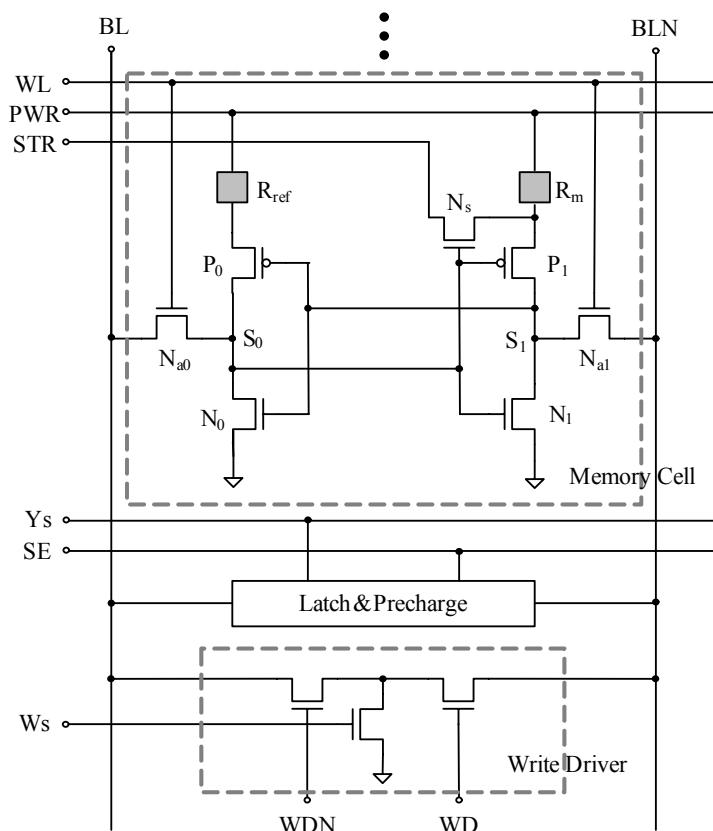

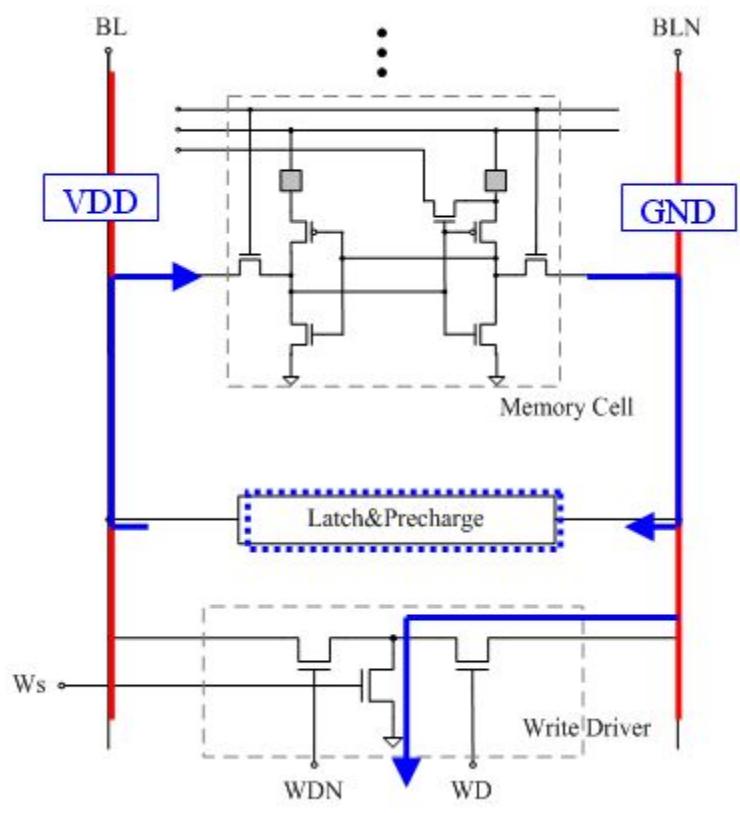

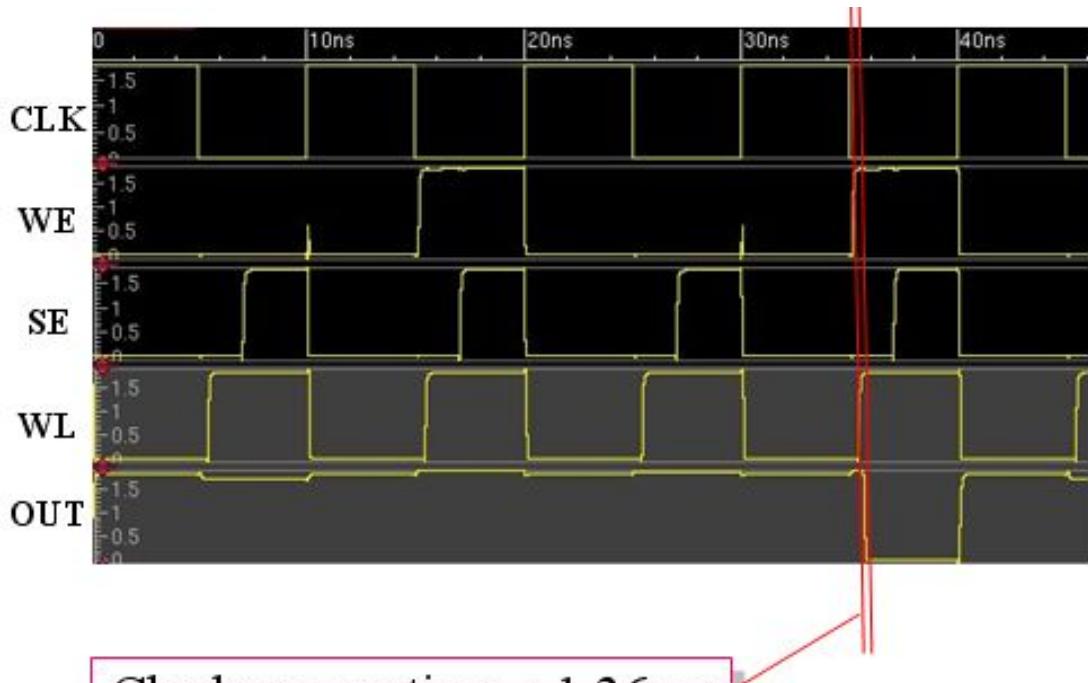

#### 5-3-4 読み出し／書き込み動作 (SRAM動作)

図 5-9に読み出し／書き込み回路を示す。

読み出し動作にはパービットセンスアンプ方式[51]を応用した。

読み出し／書き込み共に、列選択信号  $Y_s$  によってブロック単位で行われる。

図 5-9 読み出し／書き込み回路

図 5-10 読み出し動作

読み出し動作は以下の手順で行われる。

- 1) ビット線は  $Y_s$  により制御されたプリチャージトランジスタが接続されており、選択されない限りは常にチャージされている。

- 2)  $Y_s$  で 1 ブロック領域が指定され、行デコーダより WL 選択されることで、ブロック内の選択されたメモリセルがビット線対に接続される。その後、ビット線対のどちらか一方がメモリセル内トランジスタ  $N_0$ ,  $N_1$  を通じ、ディスチャージされる。遅れて信号線 SE が High となった瞬間、ビット線対に接続されたクロスカップルドラッチ回路がビット線電位差を增幅し、ディスチャージ速度を早める。各ビット線に接続されたセレクタ回路により、出力データが決定される。

この読み出し動作に際し、相変化素子を通じた電流パスは形成されない為、素子が挿入した事による動作速度の損失や記録材料疲労への影響は見られない（図 5-10 参照）。

書き込みの手順については次の通りである。

- 1) データ線 WD には書き込みデータ、WDN にはその反転電圧が入力される。また、信号線 WS は書き込み制御信号である。

- 2) プリチャージされたビット線対の片方をこのドライバでプルダウンすることによって書き込みが行われる。この時、前述の読み出し時に用いたラッチ回路を使用する。これにより、書き込み動作を高速化すると共に、記録素子に電流を流すことなく、書き換えチャージをビット線対から行い、相変化素子への影響を抑えている。

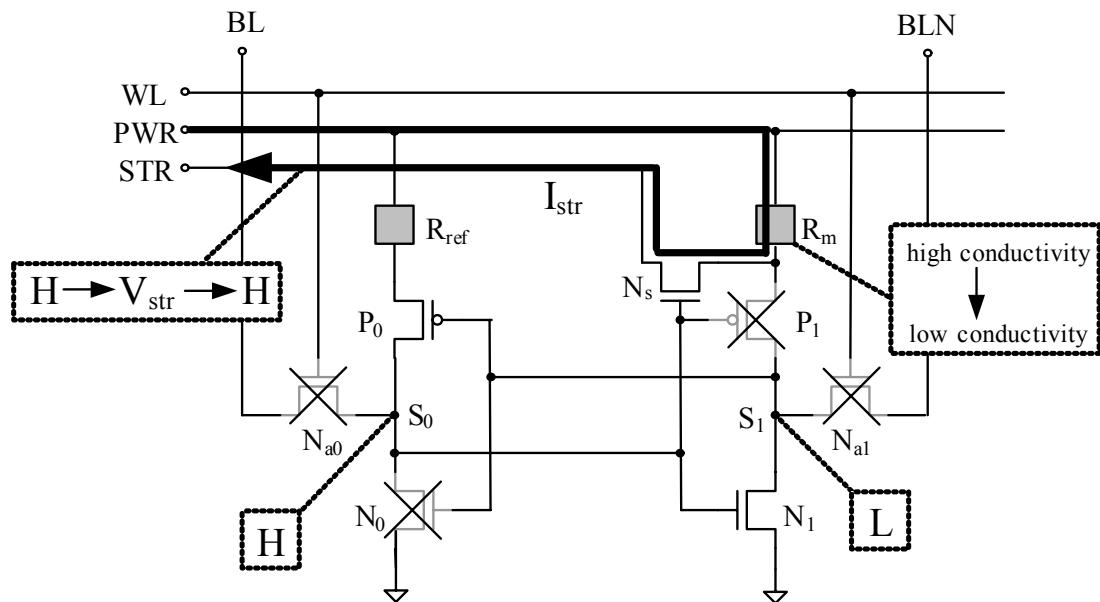

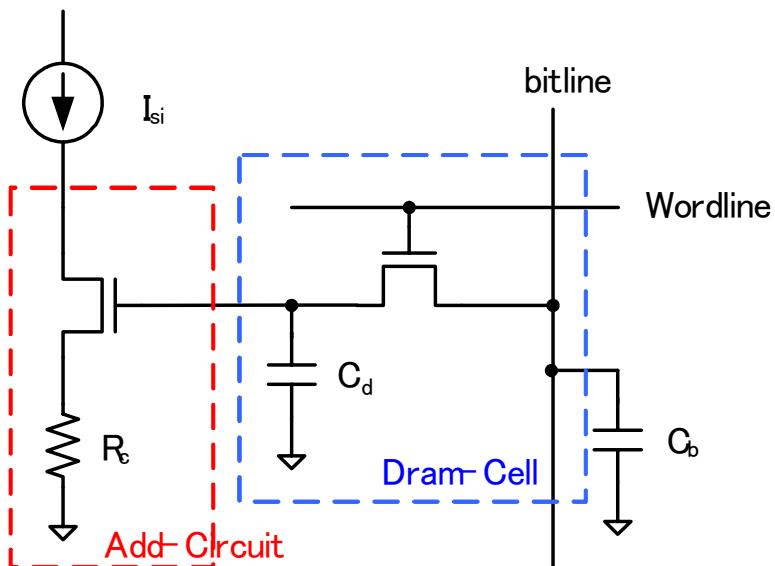

### 5-3-5 ストア動作

図 5-11 ストア動作

図 5-11にストア動作時のメモリセルを示す。基本的な動作手順は初期化動作と変わらない。初期化動作が論理値 1 を保持しているメモリセル内の記憶抵抗  $R_m$  を高抵抗状態から低抵抗状態へと遷移させるのに対し、逆の状態遷移動作を図っている。実際、初期化動作と異なるのは、素子へと加える電流量と印加時間である。高抵抗状態にするには、素子を瞬間に融点以上に過熱し、急冷する必要がある。回路では不揮発書き込み線STRを図 5-8中の  $V_{init}$ よりも低い電圧である  $V_{str}$  とすることで、PWR-STR信号線間の電位差を広げ、素子へより高振幅電圧の印加を行う。

以上の過程を経て、1 を保持するメモリセルは記憶抵抗  $R_m$  を高抵抗状態になり、電源オフ/スタンバイ状態の間保持されることとなる。また、論理値 0 ( $S_0 : L, S_1 : H$ ) が呼び出されたメモリセルでは、これも初期化動作と同様に  $N_s$  はオフである為、STR線の電圧が変化しても、 $R_m$  に電流が流れることはない。これによって、無駄な書き込み動作が抑えられ、50%の消費電力削減効果がある。

## 5-4 回路設計

### 5-4-1 仕様

表 5-2 デバイスパラメータ

|                              |                        |

|------------------------------|------------------------|

| Phase change material        | GeSbTe                 |

| Aria on-plug cell            | $(0.16 \mu\text{m})^2$ |

| Crystalline state resistance | $10\text{k}\Omega$     |

| Amorphous state resistance   | $100\text{k}\Omega$    |

| Threshold voltage            | 2.4V                   |

| Initialize required current  | $1\mu\text{A}$         |

| Initialize required time     | 100ns                  |

| Store required current       | $50\mu\text{A}$        |

| Store required time          | 15ns                   |

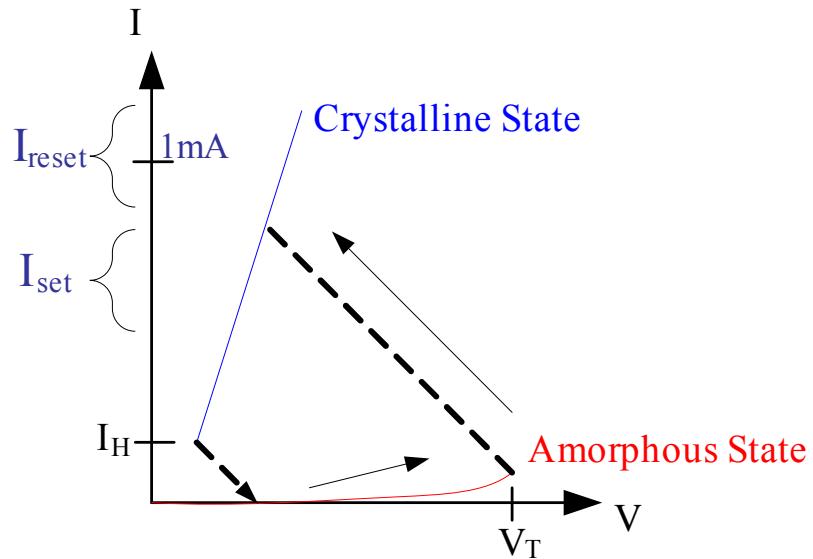

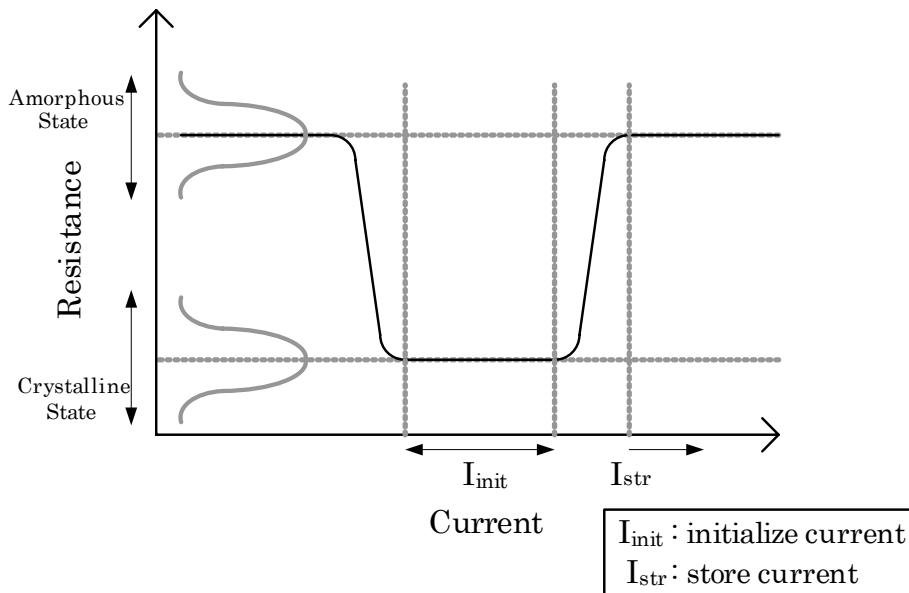

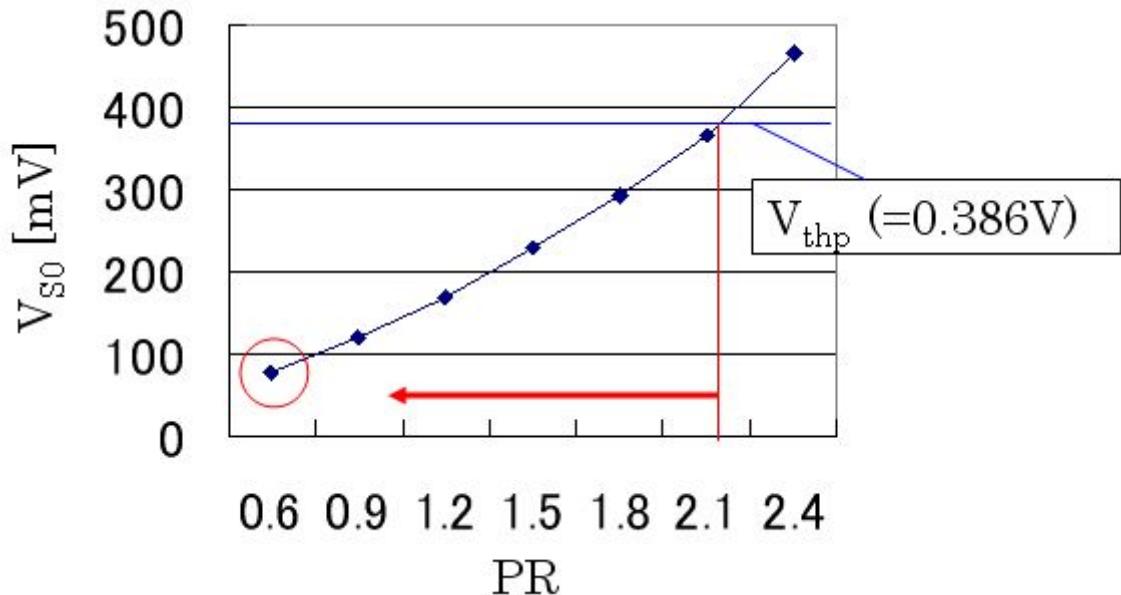

図 5-12 抵抗-電流特性図

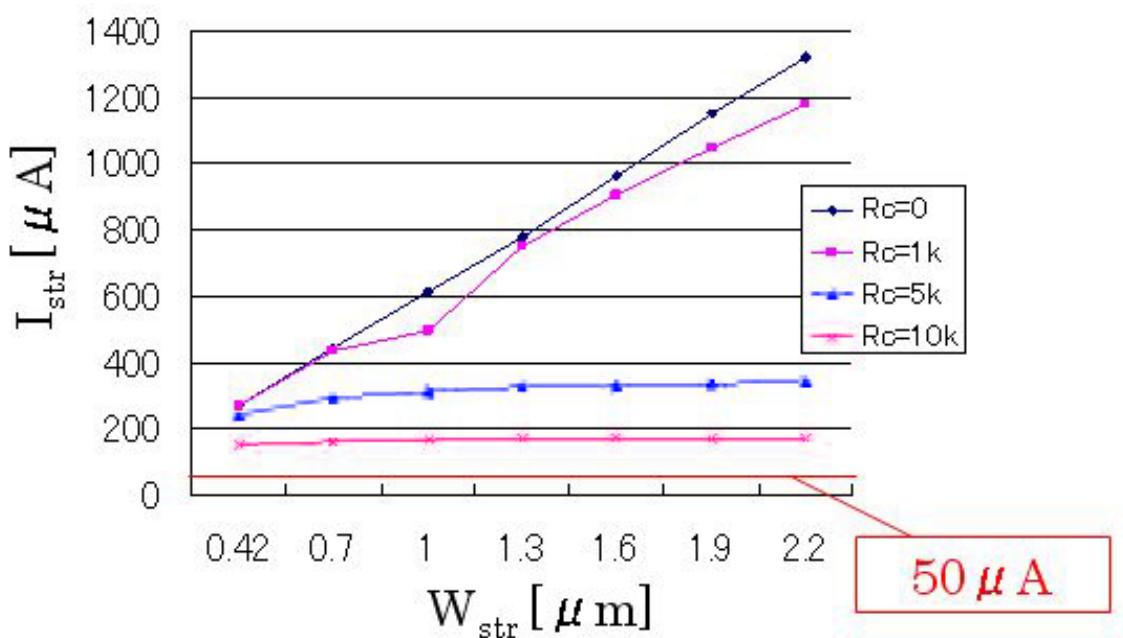

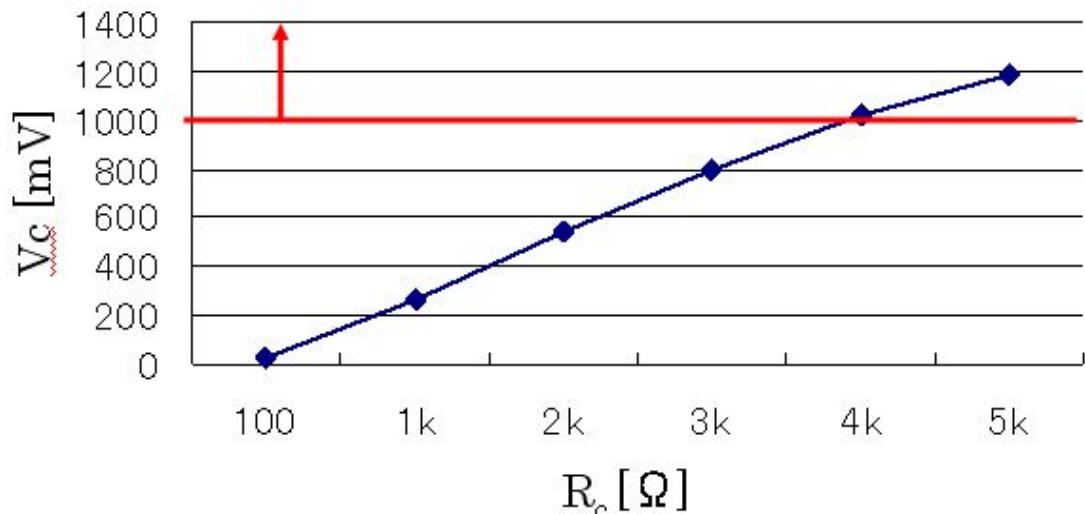

本メモリセルの設計には、文献[42]の値を参考にしている。表 5-2に得られたデバイスパラメータを示す。ここで改めて、デバイスパラメータより導かれた状態遷移の条件について述べる。

図 5-12に相変化素子における一般的な抵抗-電流特性図を示す。結晶状態から非晶質状態への遷移過程に必要電流( $I_{\text{str}}$ )条件は、相変化素子が融点に至れば良い為、デバイスパラメ

ータより  $50\mu\text{A}$  以上の電流を素子へ印加すれば良い。対して、非晶質状態から結晶状態への遷移過程において、数  $\text{M}\Omega$  以上にもなる非晶質状態抵抗に電流を流し、相変化素子を結晶化温度に保つのは困難である。そこで、カルコゲナイト半導体が有するスイッチング現象と呼ばれる特性を用いる。この現象はカルコゲナイト半導体素子に印加される電圧値が組成等毎に定まった閾値を超えてしまった場合に生じ、どのような高抵抗状態であっても、一時的に低抵抗となるものである。この現象を用いて、低電圧で電流を印加することが可能となる。この条件から結晶化相遷移に必要な電流( $I_{\text{init}}$ )の下限が定まる。デバイスパラメータより、この時の素子に印加される電圧値は  $1.1\text{V}$ 、電流値は  $1\mu\text{A}$  と定まる。なお、 $I_{\text{init}}$  が大きすぎると、再非晶質化を起こす可能性があるため、 $I_{\text{init}}$  の範囲はデバイスパラメータより  $1\mu\text{A} \sim 50\mu\text{A}$  となる。この条件を基に設計を行う。

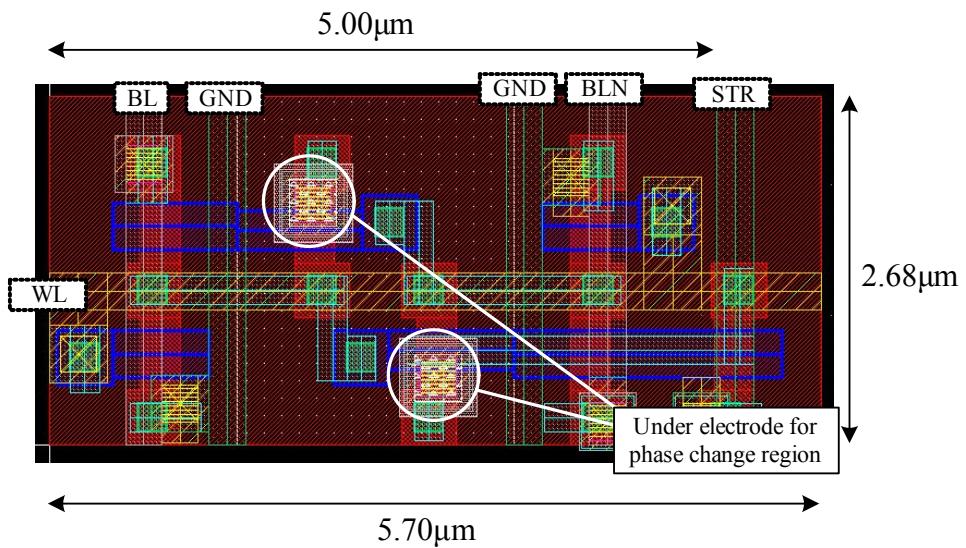

#### 5-4-2 メモリセル設計

図 5-13 PNSRAM メモリセル

図 5-13に作成したPNSRAMメモリセルプロット図を示す。セルレイアウトには、CMOS 0.18umプロセス以降の製品に適していると言われる横長SRAM構造を採用した[43]。セルサイズは  $5.70\text{um} \times 2.68\text{ um}$  となり、対して、同プロセスにおいて作成したSRAMメモリセルレイアウトでは  $5.00\text{ um} \times 2.68\text{ um}$  となった。レイアウト中央、上下にP型トランジスタのソースから最上位メタル層まで配線されている部分のが、実際にカルコゲナイト半導体膜層と接する下部電極である。記録膜はチップ上部に形成され、集積度を圧迫することがない。この為、ほぼ追加回路要素はトランジスタNsのみであり、面積オーバーヘッドは14%と見積もられた。

またここで、参照抵抗 $R_{ref}$ の抵抗値の設定もメモリ回路動作を決める重要なファクターである。しかし、これをチップ内部回路で調整を行うと、設定回路のトランジスタ素子サイズのバラツキによる抵抗値差や、制御回路を導入する上で面積、制御線、抵抗値設定時間など余計なコストがかかる。そこで、製造時に相変化膜蒸着時の温度を設定することで、蒸着時の組成配分が均等になり、膜全域において等状態(抵抗)を実現することが出来る。後は回路側にて、記録層との接合面積の調整、もしくは配線幅を変える等で調整する。

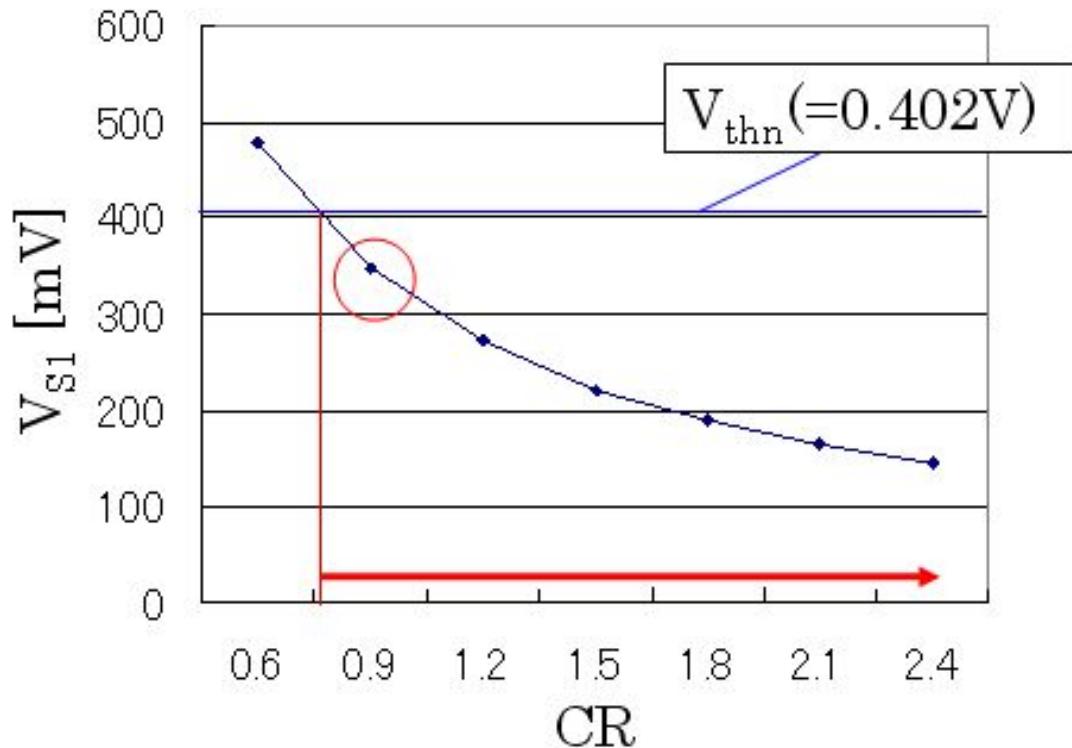

### 5-4-3 リコール安定化設計

リコール動作を行うまでの懸念事項にスイッチング現象が挙げられる。この現象が生じると正確に想起することが出来なくなる。この点を留意し、低電源で動作を行わなければならぬ。今回、本論文で想定している不揮発性素材であるGeSbTeはスイッチング電圧が約1.1Vを想定しているので、その以下の電圧 $V_{cell}$ (e.g. 1.0V)でリコール動作を行えば影響は無い。

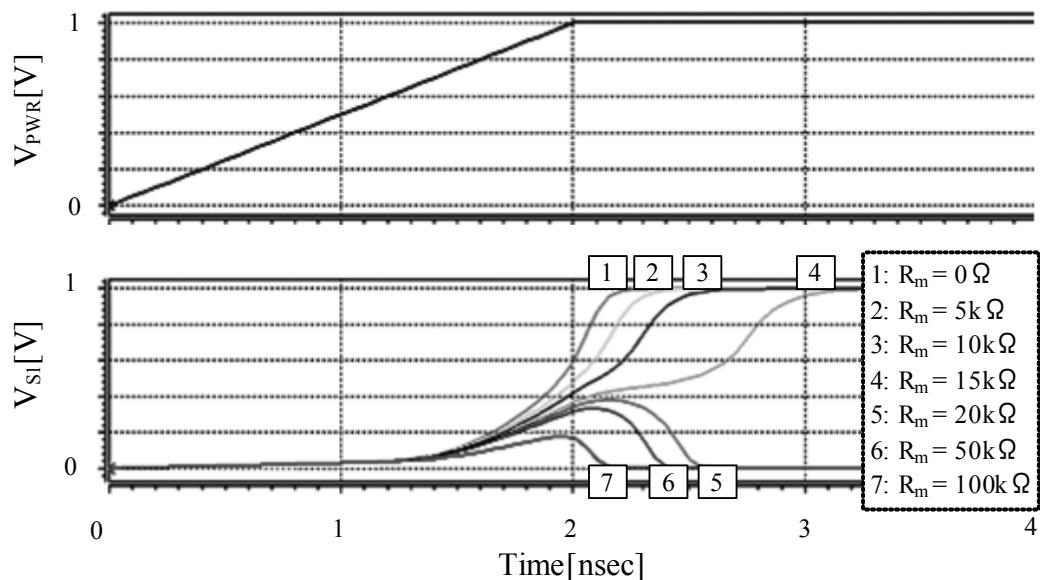

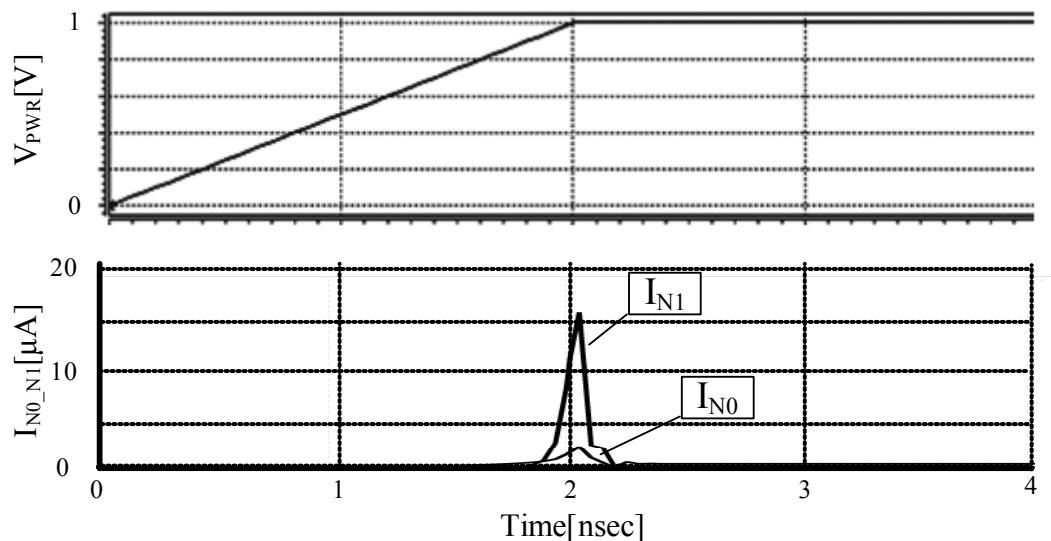

図 5-14 リコール動作シミュレーション波形