10 GHz bandwidth of Si avalanche photodiode fabricated by standard 0.18  $\,\mu\,m$  CMOS process

| メタデータ                                          | 言語: eng                           |

|------------------------------------------------|-----------------------------------|

|                                                | 出版者:                              |

|                                                | 公開日: 2017-10-03                   |

|                                                | キーワード (Ja):                       |

|                                                | キーワード (En):                       |

|                                                | 作成者:                              |

|                                                | メールアドレス:                          |

|                                                | 所属:                               |

| URL                                            | https://doi.org/10.24517/00009144 |

| This work is licensed under a Creative Commons |                                   |

This work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 3.0 International License.

# 10 GHz bandwidth of Si avalanche photodiode fabricated by standard 0.18 μm CMOS process

Koichi Iiyama<sup>1</sup>, Toshiyuki Shimotori<sup>1</sup>, Ryoichi Gyobu<sup>1</sup>, Takuya Hishiki<sup>1</sup>, and Takeo Maruyama<sup>1</sup> <sup>1</sup>Kanazawa University, Kanazawa, Japan

## Paper Summary

Silicon avalanche photodiode was fabricated by  $0.18\mu m$  CMOS process and was characterized. The bandwidth of 10GHz with the sensitivity of 0.1A/W was achieved with the electrode spacing of  $0.84\mu m$  and the detection area of  $10x10\mu m^2$ .

#### Introduction

Short-distance optical data transmission has been widely studied for realizing board-to-board and chip-to-chip high-speed data transmissions. In these applications, short wavelength vertical cavity surface emitting lasers (VCSELs) and Si photodiodes (PDs) are used for lowcost system configuration. Si PDs fabricated by complementary metal oxide semiconductor (CMOS) process are promising optical devices for easy integration with electronic circuits without any process modification, and avalanche photodiode fabricated by CMOS process (CMOS-APD) has been developed for optical interconnection applications [1-5]. The CMOS-APDs with the bandwidth over 1 GHz and the avalanche gain of more than 100 have been proposed and realized.

Here we report a CMOS-APD with 10 GHz bandwidth with 0.05 A/W responsivity and the gain-bandwidth product of 350 GHz.

### Structure

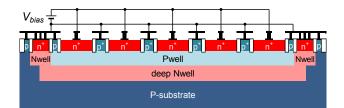

Figure 1 shows the structure of the CMOS-APD fabricated by a standard 0.18 µm CMOS process. The device is triple-well structure and is the same with nMOS structure on a p-substrate. The n<sup>+</sup>- and p<sup>+</sup>-layers are alternatively arranged and then the electrodes are interdigital structure. The light is illuminated from the top of the device. Since the P-substrate and the deep Nwell are electrically shorted, the photogenerated holes generated there move to the  $p^+$ -layers on the P-substrate, and the photo-generated electrons generated there move to the n<sup>+</sup>-layers on the Nwell, which are recombined and don't contribute to the photocurrent. This structure is very useful for high-speed operation because the transit speed of the carriers photogenerated in the deep Nwell and the substrate is very slow due to weak electric field. As a result, the photogenerated carriers generated in the Pwell and the  $n^+$ -layers on the Pwell contribute to the photocurrent.

We have fabricated CMOS-APDs for the purpose of high-speed operation, and we reported 7 GHz bandwidth of the CMOS-APD with the detection area  $S_{PD} = 20 \times 20 \ \mu\text{m}^2$  and the PAD size for RF probing  $S_{PAD} = 80 \times 70 \ \mu\text{m}^2$  [6]. The bandwidth is enhanced with

Fig.1: Typical structure of a CMOS-APD.

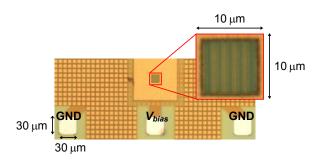

Fig.2: Photograph of fabricated CMOS-APD.

decreasing the electrode spacing  $L_S$  due to decreased carrier transit time, and is also enhanced with decreasing the detection area and the PAD size for RF probing due to decreased depletion capacitance and the PAD capacitance, respectively. In this study, we fabricated the CMOS-APD with the electrode spacing  $L_S = 0.84 \,\mu\text{m}$ and 1.00  $\mu\text{m}$ , the detection area  $S_{PD} = 10 \, \text{x} \, 10 \,\mu\text{m}^2$  and the PAD size for RF probing  $S_{PAD} = 30 \, \text{x} \, 30 \,\mu\text{m}^2$ , which is the minimum size for RF probing, to further enhance the bandwidth. The photograph of the fabricated CMOS-APD is shown in Fig. 2.

## Characterization

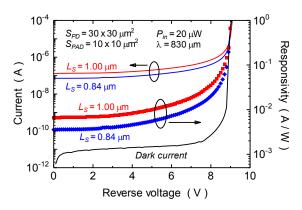

Figure 3 shows the I-V characteristics (left axis) of the CMOS-APD. The dark current at a low bias is about 10 pA, and the breakdown voltage is 9.1 V. Under light illumination ( $\lambda = 830$  nm, 20 µW), the current is almost constant for the bias voltage below 6 V, and is gradually increased; especially when the bias voltage is above 8 V, the current is significantly increased due to avalanche amplification, which occurs around the interface between the Pwell and the n<sup>+</sup>-layers. The photocurrent of the CMOS-APD with the electrode spacing  $L_S = 0.84$  µm is lower than that with  $L_S = 1.00$  µm because the increased number of electrodes block the light incident into the device.

Fig. 3: Measured I-V charactristics and responsivity of the CMOS-APD.

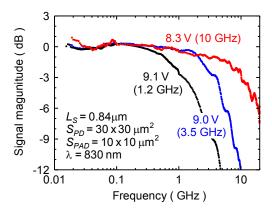

Fig. 4: Frequency response of the CMOS-APD.

The responsivity is also shown in Fig. 3 (right axis). The responsivity at 0 V bias is 3.6 mA/W and 6.6 mA/W for  $L_S = 0.84 \,\mu\text{m}$  and  $L_S = 1.00 \,\mu\text{m}$ , respectively, and is increased due to the avalanche amplification, and the responsivity of about 1.0 A/W was achieved about 9 V bias voltage.

Figure 4 shows the frequency response of the CMOS-APD with the electrode spacing  $L_S = 0.84 \,\mu\text{m}$ . In the measurement, a laser light with the wavelength of 830 nm is intensity modulated by an electro-optic modulator with the bandwidth of more than 25 GHz, and the frequency response of the modulator and RF cables are compensated by using a commercial GaAs PIN photodiode with the nominal bandwidth of 30 GHz. The largest bandwidth of 10 GHz is achieved at 8.3 V.

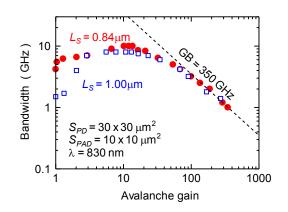

Figure 5 is the relationship between the bandwidth and the avalanche gain. The bandwidth is maximized when the avalanche gain is about 10, and the maximum bandwidth of 10 GHz is achieved for the electrode spacing  $L_s = 0.84 \,\mu\text{m}$ . The gain-bandwidth product is 350 GHz for the two CMOS-APDs. Since the responsivity of the CMOS-APD at 0 V bias is quite low as is shown in Fig. 3, the responsivity under avalanche amplification is also low regardless of large avalanche gain. We also plot the bandwidth against the responsivity in Fig. 6. The maximum bandwidth of 10 GHz is

Fig. 5: Bandwidth against avalanche gain.

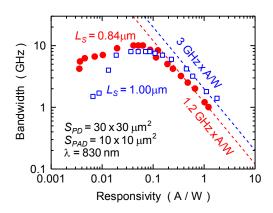

Fig. 6: Bandwidth against responsivity.

obtained with the sensitivity of around 0.05A/W. The bandwidth-responsivity product is 3.0 GHz x A/W and 1.2 GHz x A/W for the CMOS-APD with the electrode spacing  $L_S = 1.00 \ \mu\text{m}$  and  $L_S = 0.84 \ \mu\text{m}$ , respectively.

#### Conclusions

The CMOS-APD with 10 GHz bandwidth and 0.05 A/W responsivity is realized by narrowing the electrode spacing and decreasing the detection area and the PAD size for RF probing.

## Acknowledgement

The CMOS-APD was fabricated in the chip fabrication program of VLSI Design and Education Center (VDEC), the University of Tokyo, in collaboration with Rohm Corporation and Toppan Printing Corporation.

#### References

- 1. W.-K. Huang et al, IEEE Photon. Technol. Lett., 19 (2007), p. 197.

- 2. H.-S. Kang et al, Appl. Phys. Lett., 90 (2007) 151118.

- K. Iiyama et al, IEICE Trans. Electron., E91-C (2008), p. 1820.

- 4. M.-J. Lee et al, Opt. Express, 18 (2010), p. 24189.

- K. Iiyama et al, IEEE Photon. Technol. Lett., 22 (2010), p. 932.

- T. Shimotori et al, OECC 2013, Kyoto, Japan (2013) MM1-3.